Better Late Than Never: Magical Verification Horizons DAC Edition

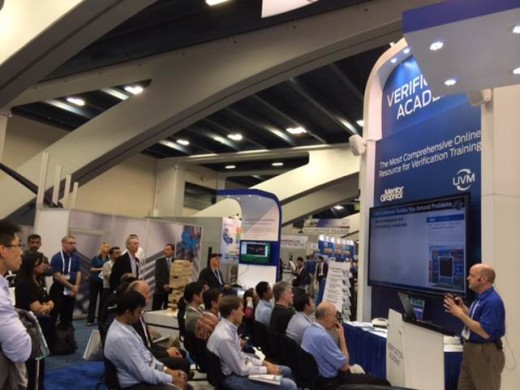

As some of you may have seen, we release a great DAC edition of Verification Horizons back in June. Unfortunately, we were so focused on preparing for a great Verification Academy Booth at DAC

that I completely forgot to blog about the issue! Well, as the saying goes, “better late than never.” In particular, I’d like to call your attention to two articles.

The first is “Best Practices for FPGA and ASIC Development” by my Mentor colleagues Josh Rensch and John Boone, in which they take you through the four development phases of an FPGA project. By separating the process into distinct PLAN, EXECUTE, VERIFY and SUPPORT phases, Josh and John help you establish a manageable process that you can apply to your next project. The key is to identify the techniques, or specific activities, that will be used at each phase, and establish a rigorous set of deliverables for each phase. Just like clear interface specs are necessary for two design blocks to be able to talk to each other, clear deliverables at each phase of the process let different groups work together efficiently to create a robust and well-verified design.

The other article I wanted to point out to you is “Merging SystemVerilog Covergroups by Example” by our friend Eldon Nelson, a verification engineer at Micron Technology. This article explores the options available when defining and using covergroups, establishing some important guidelines that will help you get the most useful information when multiple instances of covergroups are merged together. Be sure to check it out.

The other articles in the issue are:

- Visualizer™ Debug Environment: Class-based Testbench Debugging using a New School Debugger – Debug This!

by Rich Edelman, Verification Technologist, Mentor Graphics - Optimizing Emulator Utilization

by Russ Klein, Program Director, Mentor Graphics - MIPI LLI Verification using Questa Verification IP

by Vaibhav Gupta, Lead Member Technical Staff and Yogesh Chaudhary, Consulting Staff, Mentor Graphics - Stories of an AMS Verification Dude: Model Shmodel

by Martin Vlach, PhDude, IEEE Fella, Chief Technologist AMS, Mentor Graphics - Functional Coverage Development Tips: Do’s and Don’ts

by Samrat Patel, ASIC Verification Engineer, and Vipul Patel, ASIC Engineer, eInfochips - Increasing Verification Productivity Through Functional Coverage Management Automation

by Gunjan Gupta and Anand Shirahatti, CTO, Arrow Devices - Use of Iterative Weight-Age Constraint to Implement Dynamic Verification Components

by Mahak Singh, Design Engineer, Siddhartha Mukherjee, Sr. Design Engineer, Truechip - UVM Testbench Structure and Coverage Improvement in a Mixed Signal Verification Environment

by Mihajlo Katona, Head of Functional Verification, Frobas