Prologue: The 2010 Wilson Research Group Functional Verification Study

Study Overview

In 2002 and 2004, Ron Collett International, Inc. conducted its well known ASIC/IC functional verification studies, which provided invaluable insight into the electronic industry’s state and trends in design and verification at that point in time. However, after the 2004 study, no other industry studies were conducted, which left a void in identifying industry trends.

To address this void, Mentor Graphics commissioned Far West Research to conduct a new industry study on functional verification in the fall of 2007. The study was conducted as a blind study to avoid influencing the results. This means that the survey participants did not know that the study was commissioned by Mentor Graphics. In addition, to support trend analysis on the data, the survey followed the same format and questions that were asked in the 2002 and 2004 Collett studies.

In the fall of 2010, Mentor Graphics commissioned Wilson Research Group to conduct a new functional verification study. This study is a blind study and follows the same format as the Collett and Far West Research studies. The 2010 Wilson Research Group study is one of the largest functional verification studies ever conducted. It is about 3.5 times larger than the Collett studies, and twice as large as the Far West Research study. The overall confidence level of the study was calculated to be 95% with a margin of error of 4.1%.

Unlike the previous Collett and Far West Research studies that were conducted in North America only, the 2010 Wilson Research Group study is a worldwide study. The regions targeted are:

- North America: Canada, United States

- Europe/Israel: Finland, France, Germany, Israel, Italy, Sweden, UK

- Asia (minus India): China, Korea, Japan, Taiwan

- India

The survey results are compiled both globally and regionally for analysis.

Another difference with this study is that it includes FPGA engineers. I decided when I started to process the study results that I would compile both with the combined FPGA and non-FPGA data (when appropriate) and also separately for analysis. Obviously, for trend analysis I can only show the non-FPGA (IC/ASIC) data since no previous study included FPGA participants.

When compiling and analyzing the data from the study, in addition to calculating the mean on various aspects of the data, I decided to calculate the median for trend analysis. My objective in calculating the median is that the resulting value partitions the data into equal halves, which at times is more insightful when discussing trends.

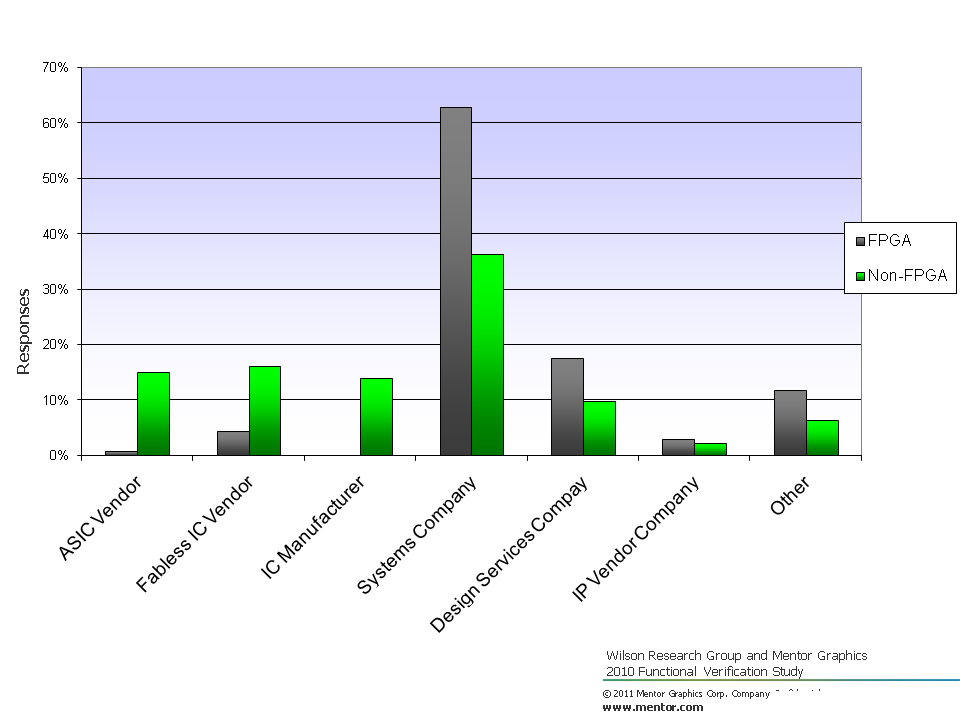

Figure 1 shows the percentage makeup of survey participants by the company type. The grey bars represents the FPGA participants while the green bars represents the non-FPGA (i.e., IC/ASIC) participants.

Figure 1: Survey participants company description

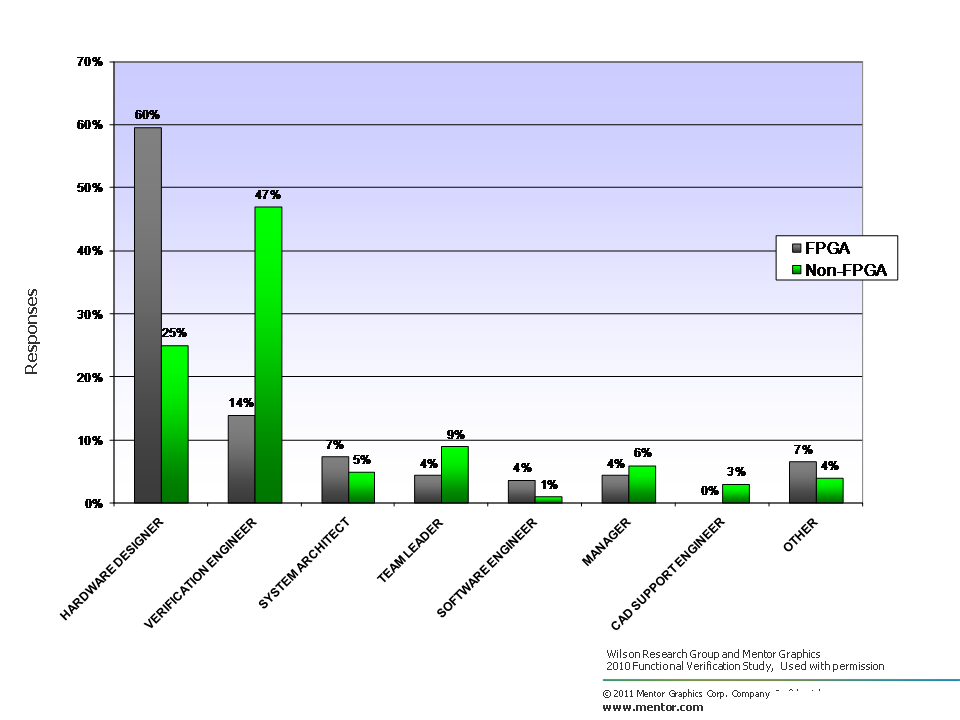

Figure 2 shows the percentage makeup of survey participants by their job description. Again, the grey bars represents the FPGA participants while the green bars represents the non-FPGA (i.e., IC/ASIC) participants.

Figure 2: Survey participants job title description

In a future set of blogs, I plan to present the highlights from the 2010 Wilson Research Group study along with my analysis, comments, and obviously, opinions. A few interesting observations emerged from the study, which include:

- Reuse adoption is increasing.

- The effort spent on verification is increasing.

- The industry is adopting more advanced functional verification techniques.

My next blog (click here) presents current design trends that were identified by the survey. This will be followed by a set of blogs focused on the functional verification results.

Quick links to the 2010 Wilson Research Group Study results (so far…)

- Part 1 – Design Trends

- Part 2 – Design Trends (Continued)

- Part 3 – Reuse

- Part 4 – Effort Spent In Verification

- Part 5 – Effort Spent In Verification (Continued)

- Part 6 – Testbench characteristics and Simulation Strategies

- Part 7 – Testbench characteristics and Simulation Strategies (continued)

- Part 8 – Language and Library Trends

- Part 9 – Verification Techniques and Technologies Adoption Trends

More to come!!!

Comments