Tessent at the 2021 AI Hardware Summit

Don’t miss the AI Hardware Summit from September 13-16, 2021. The summit is THE place for those accelerating

AI workloads in at the cloud and at the edge, at both a hardware and systems level. This hybrid (live/virtual) event

will be held in Mountain View, CA and on your computer screen from anywhere in the world.

As proud sponsors of this year’s AI Hardware Summit, we can offer an additional 10% saving when you use our discount code SIEMENS10.

Register now!

Arrange to see a Demo / book a meeting

Tessent’s Gajinder Panesar, Siemens Fellow, helps kick start the summit on Monday, September 13.

Tessent’s Gajinder Panesar, Siemens Fellow, helps kick start the summit on Monday, September 13.

Gajinder will present in the inaugural AI Hardware Design Lab, which will feature leading technology providers proteanTecs, Siemens and Synopsys. The trio of presentations focuses on how to maximize the performance of AI hardware via chip design best practices, smart monitoring, and on-chip analytics for AI hardware both in design and in production. If you’re a chip designer or architect, this is a must-attend session to stay on top of the leading tools and techniques for ensuring durable, reliable and performant products for your customers.

The move to AI and ML-type workloads has created an explosion in SoC complexity, as developers try to find a balance between speed, cost, and application flexibility. The challenge goes well beyond the problem of debugging the compute cores, dimensioning interconnects and refining the performance of memory controllers. Today’s chip development teams, software developers and systems integrators need good quality information

about the functional behavior of devices.

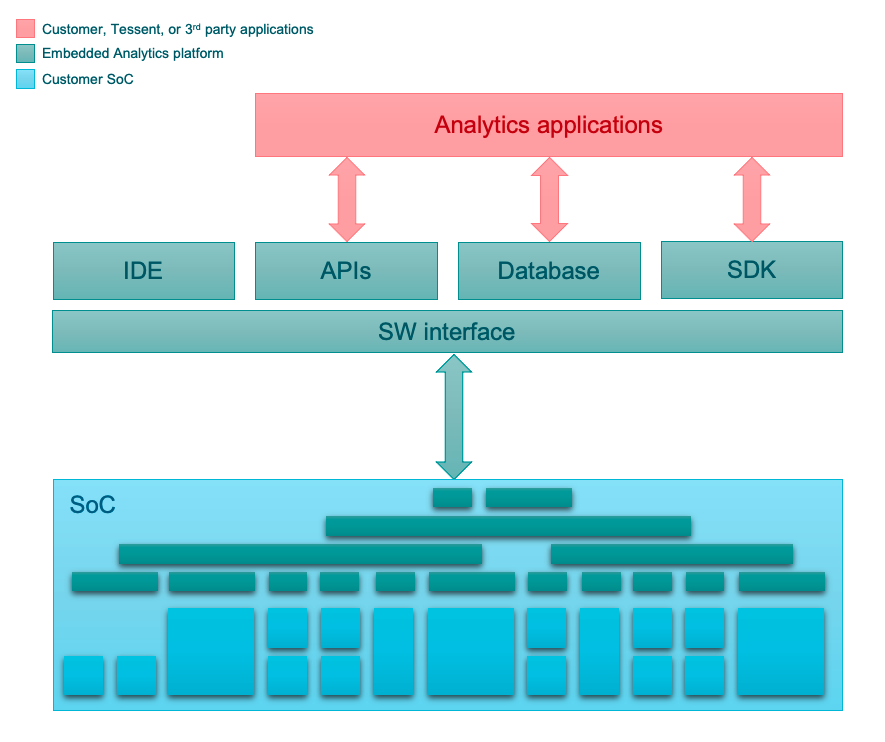

A functional data-gathering and analytics infrastructure can give both fine-grained information on the chip’s behavior under real operating conditions, and system-level visibility of the functional operation of the entire device.

This presentation will demonstrate the use of on-chip functional monitoring to solve some of these tricky development and validation problems. With direct examples drawn from customer experience, we will examine how AI chip designs can be more quickly and efficiently validated, debugged, deployed and optimized, both before market launch and during the full lifetime of the device.

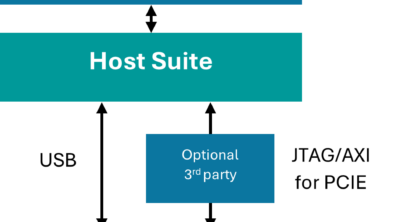

In the Siemens exhibitor booth, we will demonstrate how the Tessent Embedded Analytics platform gives you unparalleled visibility and insights into complex functional behavior of your AI SoC. We will show you how to generate unique and valuable insights into system performance, under real software loads, from emulation and into deployment, by combining our silicon IP portfolio, our software toolset and powerful data analytics libraries.

While you are there, you can enter a drawing to win a Bose speaker (one winner per in-person event day).

To optimize AI system performance, you need a deep understanding of how your AI hardware functions under real firmware and software loads, starting from the development phase and into the life of the product. This means that you need access to the right functional data from the chip and powerful software tools to process it. The Tessent Embedded Analytics platform provides this kind of system-level visibility for SoCs. In this short demo, we will introduce you to our silicon IP and software tools. We will demonstrate how you can collect relevant functional data from your AI SoC using Embedded Analytics on-chip monitors and show how to explore and analyze the data to surface unique operational insights which would otherwise be out of reach. You will learn how you can use our powerful analytics toolkit to drive performance even higher by finding bottlenecks and optimizations for your system.

For more information on optimizing AI systems with Embedded Analytics, download the technical paper here:

Harness system-level data to optimize manycore AI and ML chips