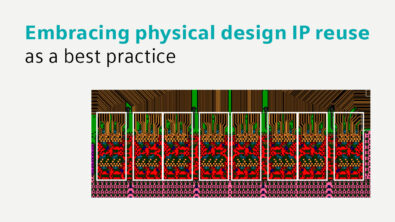

Embracing physical design IP reuse as a best practice

Efficiency in IC package design is becoming more important as design cycles shorten and complexity surges. One common approach to achieving efficiency is through the reuse of physical design intellectual property (IP). However, the conventional method of cut-copy-paste, while simple, has significant limitations. Understanding these limitations and exploring advanced methods of IP reuse can lead to substantial time savings and higher-quality designs.

The limitations of cut-copy-paste

At its core, cut-copy-paste is a straightforward method of reusing design elements. Designers take a section of an existing design and replicate it in a new context. While this method is acceptable in some scenarios, it often falls short because manual manipulation of the netlist can introduce errors that are difficult to detect and rectify. Tracking changes back to the golden source of data also becomes challenging, leading to potential discrepancies and quality issues. This method is also labor-intensive and can increase the risk of human error, slowing down the design cycle.

These limitations highlight the need for a more robust and reliable approach to IP reuse, especially in complex IC package designs.

The power of physical design reuse circuits (PhRCs)

Physical design reuse circuits (PhRCs) offer a sophisticated solution to the challenges of traditional IP reuse. PhRCs are first-class design objects that are built for seamless reuse, providing numerous advantages over the cut-copy-paste method:

- Dynamic net propagation: PhRCs allow for the automatic propagation of nets from the parent netlist, reducing the need for manual intervention.

- Rapid ECOs: Engineering Change Orders (ECOs) can be implemented quickly and efficiently, ensuring that design updates are easily managed.

- Golden source management: PhRCs help maintain the integrity of the golden source of verified design content, ensuring consistency and reliability.

- Modularity: PhRCs promote modularity in design, enabling easier collaboration across designs, designers, and teams.

Practical applications of PhRCs

Most IC package designs feature areas of symmetry that are ideal for reuse. Examples include:

- Die-to-die routing: Standard interfaces between dies can be replicated using PhRCs, ensuring consistency and reducing design time.

- Core power and ground supply structures: Complex via arrays and power distribution networks can be standardized and reused across different designs.

- Device fanouts: Fanout patterns for various devices can be reused, ensuring optimal performance and reducing design errors.

As IC packages become increasingly complex, the need for efficient and reliable IP reuse methods becomes more critical. Physical Design Reuse Circuits (PhRCs) represent a powerful advancement over traditional cut-copy-paste techniques, offering dynamic net propagation, rapid ECOs, and robust management of golden source data. By embracing PhRCs, designers can achieve significant time savings, improve design quality, and enhance collaboration across teams. As the industry continues to evolve, leveraging advanced IP reuse methods like PhRCs will be essential for staying competitive and delivering top-notch designs.

Read about this best practice and more in our eBook: IC package physical design best practices

Comments

Leave a Reply

You must be logged in to post a comment.

I appreciate how this idea challenges conventional wisdom in a thoughtful way. Area Code