At ECS Syd – talking about memory fragmentation, power management and self-test

Each Fall, just before the weather becomes too horrible, I get to attend ECS [Embedded Conference Scandinavia] in Stockholm, Sweden. It has become a good event for embedded developers in that area and I am pleased that my paper submissions seem to result in a couple of acceptances each year.

This year, I assume ECS will be in 6 months or so, but the organizers are inaugurating a new event …

Next week [10/11 March] is ECS Syd [“syd” is Swedish for south], which is being held in Malmö in southern Sweden. This is an area where there is quite a good start-up culture, so it should be an interesting environment.

I submitted some proposals and was pleased to receive two acceptances. Then, another speaker canceled and the organizers kindly offered me a further slot, so now I have 3 sessions:

Dynamic Memory Allocation & Fragmentation in C & C++

In C and C++, it can be very convenient to allocate and de-allocate blocks of memory as and when needed. This is certainly standard practice in both languages and almost unavoidable in C++. However, the handling of such dynamic memory can be problematic and inefficient. For desktop applications, where memory is freely available, these difficulties can be ignored. For embedded – generally real time – applications, ignoring the issues is not an option.

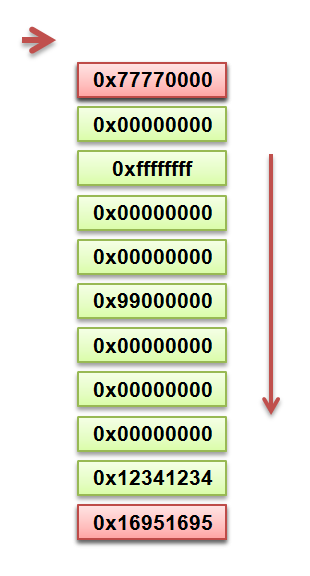

Dynamic memory allocation tends to be non-deterministic; the time taken to allocate memory may not be predictable and the memory pool may become fragmented, resulting in unexpected allocation failures. In this session the problems will be outlined in detail and an approach to deterministic dynamic memory allocation detailed.

Power Management in Embedded Systems

The importance of power management in today’s embedded designs has been steadily growing as an increasing number of battery powered devices are developed. Often power optimizations are left to the very end of the project cycle, almost as an afterthought. In this paper we will discuss design considerations that should be made when starting a new power sensitive embedded design, which include choosing the hardware with desired capabilities, defining a hardware architecture that will allow software to dynamically control power consumption, defining appropriate power usage profiles, making the appropriate choice of an operating system and drivers, choosing measurable power goals and providing these goals to the software development team to track throughout the development process.

Self-testing in Embedded Systems

All electronic systems carry the possibility of failure. An embedded system has intrinsic intelligence that facilitates the possibility of predicting failure and mitigating its effects. This paper reviews the options for self-testing that are open to the embedded software developer. Testing algorithms for memory are outlined and some ideas for self-monitoring software in multi-tasking and multi-CPU systems are discussed.

—

If you are attending this event, do stop by and say “hej”. If you would like a copy of my slides for any of the sessions, please email or contact my via one of the social networking channels.