Minimizing insertion loss: Why understanding trace width is critical at high frequencies

Material matters

An engineer asked me recently about the relationship between trace width and insertion loss while adjusting dielectric height to maintain a 50 Ohm single-ended impedance.

At a high level, there are 5 variables at work here, including trace width, copper weight, dielectric height, Dk, and Df. Include frequency and resin content, and we’re really talking about 7 variables. Then there are stripline vs. microstrip configurations, which change things a bit, as well as % copper (which impacts prepreg thickness), and copper roughness. We’ll keep things simple, for discussion’s sake, and address some of these factors in future columns.

Lossy transmission-line effects become significant signal integrity concerns at clock frequencies above roughly 1 GHz and for interconnect lengths that exceed 12 inches. Assuming that we’re talking striplines, and grabbing data from a Megtron 6 (G) stackup I was looking at today, we’ll use an insertion loss comparison between two different trace width/dielectric height combinations. (Dks are similar, but a little bit different—depending on resin content.)

Example Design

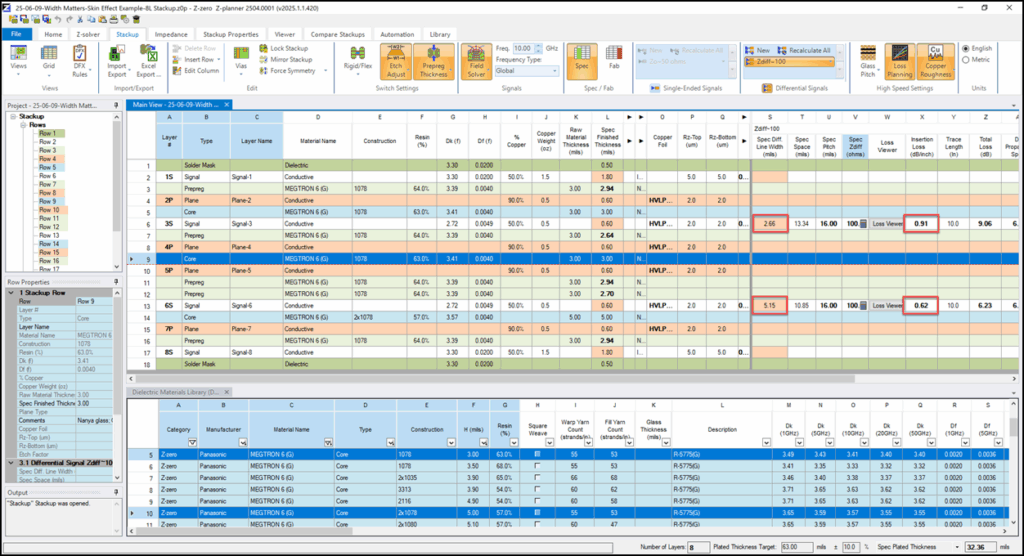

From Panasonic’s Megtron 6 (G) tables, an example 8-layer stackup provides a convenient illustration (modified for this blog post):

- Layer 3—Narrow trace width, thinner dielectrics:

- Width=2.66 mils

- Cores at 3 mils (single ply 1078 glass); half-oz. copper

- Pressed prepregs at 2.64 mils (single ply)

- Layer 6—Wider trace, thicker dielectrics:

- Width=5.15 mils

- Cores at 5 mils (dual-ply1078 glass); half-oz. copper

- Pressed prepregs at 5.64 mils (dual-ply 1078 glass)

- Electrical characteristics for dielectrics:

- Cores: Dk = 3.64 (RC=54%); Df = 0.004

- Prepregs: Dk = 3.4 (RC=63%; 1078 glass); Df = 0.003

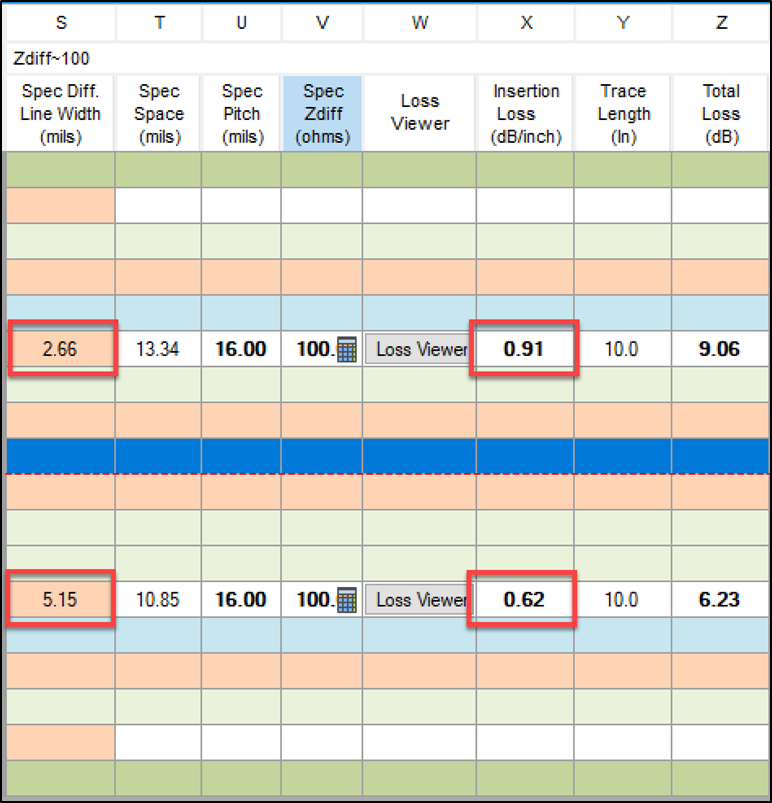

At 10 GHz, column X in Figures 1 and 2 show insertion loss computed at 0.91 dB/in. for the 2.66-mil wide trace on layer 3 and 0.62 dB/in. for the 5.15 mil line on layer 6, aligning with the conventional wisdom that a narrower trace width results in increased signal attenuation.3

Key Insertion Loss Components

In addition to copper roughness, which I covered in a recent webinar, there are two other components of insertion loss: resistive loss, the subject of this blog, and dielectric loss.

Resistive Loss: From DC through frequencies up to a few MHz, the current in a trace moves through the entire cross-sectional area of the trace. At higher frequencies, however, current flows along the perimeter of a line rather than uniformly across the entire cross section. As a result, the series resistance of the signal and return path conductors increases with the square root of frequency as the effective cross section of the interconnect path is reduced. This type of loss is often referred to as “skin effect.”

Dielectric Loss: The second important loss mechanism is dielectric loss, which is simply the conversion of electrical energy from the alternating electric field into heat. Dielectric loss is often specified in decibels per inch, increases with frequency, and varies inversely with a material’s “dissipation factor” or Df—which is a function of the material’s resin type and molecular structure. Depending on resin content, “standard loss” FR-4 materials have Dfs ranging from 0.0015-0.015.

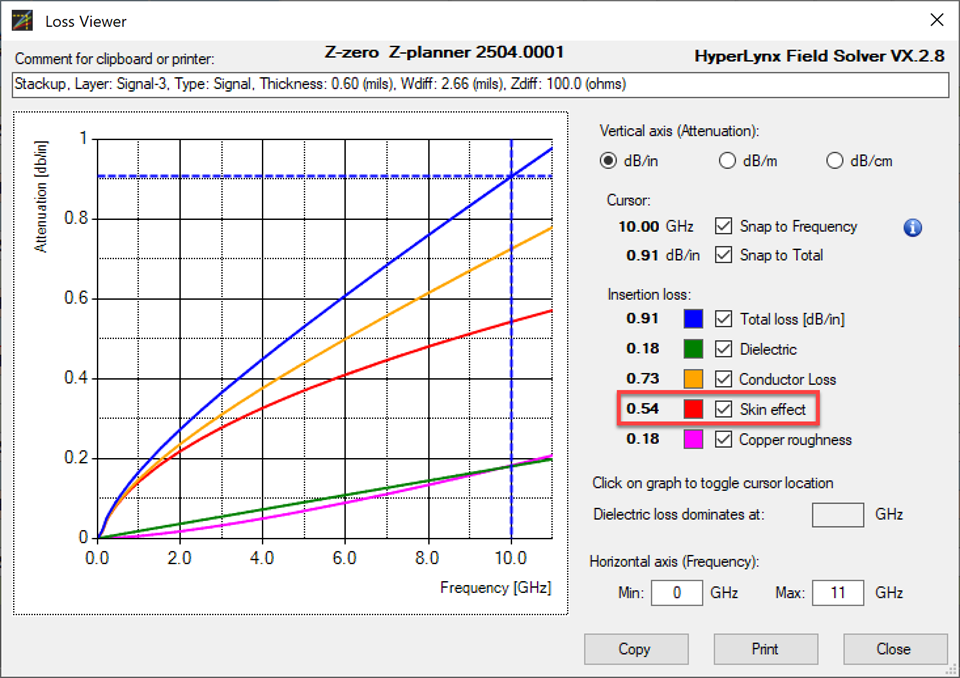

Lower Df values equate to more of the output signal getting to its destination, as well as higher material costs, as compared to standard-loss materials. Since we used similar dielectrics on both signal layers in our example, we shouldn’t expect the dielectric loss component to be much different between the narrow trace on layer 3 and the wider trace on layer 6. We can confirm this by using the Loss Viewer in Z-planner software to examine the contributions of conductor loss and dielectric loss to the overall insertion loss across these layers. Layer 3 results for the w=2.66 mil case are shown in Figure 3.

Here we can see that dielectric loss is only contributing 0.18 dB/in., while resistive loss from skin effect) is contributing a full 0.54 dB/in.—a full 3x the dielectric-loss contribution! Of course, we would want to multiply insertion-loss numbers by trace lengths to produce total channel losses, which is shown in columns Y and Z in Figure 2.

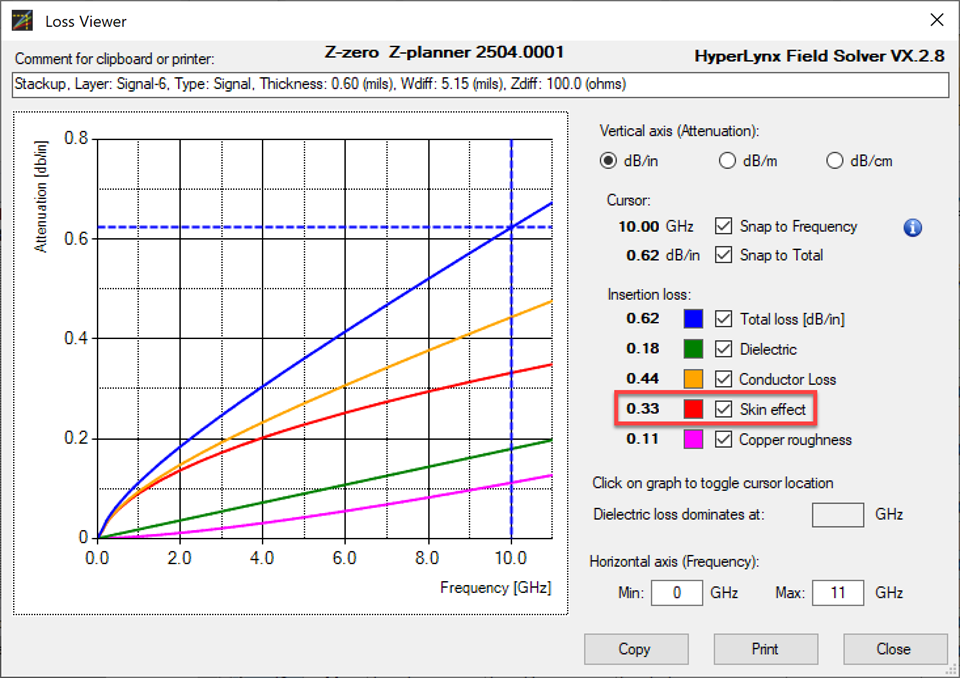

Figure 4 shows the same plot for the 5.5 mil trace on layer 6.

Here we can see that our dielectric loss hasn’t changed, while skin effect has dropped significantly—to just 0.33 dB/in. Of course, the thicker dielectrics would result in a bigger overall board thickness, but if you’re hunting for eliminating the last few dBs from an interconnect budget, it’s helpful to have gained this insight early in the design process.

Conclusions

Some say that trace width isn’t a big deal when it comes to insertion loss, but here we learned that significantly wider trace widths can be a great lever for reducing insertion loss. One of the costs associated with significantly wider traces is that the board will be thicker and proportionately more expensive. This, in fact, is a common technique for high-speed backplanes where insertion loss is a big concern, and you can afford to spend a bit more.

We could go a good bit further with this example, looking at higher-loss but lower-priced laminates. We could also explore the effect of copper roughness and resin content.

Megtron 6 (G), represents just one alternative in the range of dielectric-loss possibilities among the various laminates on the market. For an actual design, you may want to make material tradeoffs in a stackup design tool and then specifically discuss the tradeoffs with your board vendor.

I greatly encourage you to explore this relationship within your stackups with our free online trial of Z-planner Enterprise. It grants you full access to the Loss Viewer as well as our line of dielectric stackup materials. It provides you the opportunity to perform all of this comparison completely free.

Comments

Leave a Reply

You must be logged in to post a comment.

Great explanation of why trace width becomes so important at high frequencies. It’s easy to overlook how small layout decisions can significantly impact insertion loss and overall signal integrity, much like how color printer test pages reveal small issues before final output. Understanding these details really helps in designing more reliable high-frequency circuits.