ECC in Memory Test and Repair

Error Correction Codes (ECC) have long been a cornerstone of reliable memory design, primarily serving as a shield against transient faults — those fleeting, unpredictable bit flips caused by cosmic rays, voltage fluctuations, or electromagnetic interference in SRAMs. But as semiconductor technology continues to scale and emerging memory technologies introduce increasingly complex and varied defect profiles, ECC is stepping into a much broader role. Today, ECC is not just a runtime safety net; it is becoming an integral part of the manufacturing and in-system test and repair strategy, working hand-in-hand with traditional repair techniques to improve yield and ensure long-term device reliability.

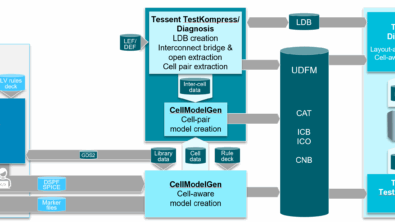

Implementing ECC-aware memory test and repair requires a highly flexible hardware architecture, capable of adapting to a wide range of design configurations. Depending on the memory architecture, the system must account for variables such as the number of correction bits available for repair, the presence or absence of spare resources like I/O or column repair elements, and whether row repair is supported. In some designs, ECC acts as a complementary mechanism alongside conventional spare-row and spare-column redundancy — enhancing overall yield by catching defects that traditional repair resources cannot address. In others, particularly where area constraints make spare resources impractical, ECC serves as the sole repair mechanism, correcting permanent faults entirely through its error correction capability rather than physical spare replacement.

This dual role of ECC — as both a functional safety feature and a yield enhancement tool — represents a significant evolution in memory design philosophy. Tools like Tessent MemoryBIST are purpose-built to support this ECC-aware test and repair paradigm, offering the flexibility to handle diverse memory configurations while seamlessly integrating ECC logic testing into the broader DFT flow. As memory arrays grow larger and defect mechanisms grow more complex, embracing ECC-aware repair strategies will be essential for achieving the yield, reliability, and functional safety targets demanded by today’s automotive, industrial, and high-performance computing applications.

For more information click here.