Boundary Scan Evolved: Enabling Hierarchical Designs with Tessent EBSCAN

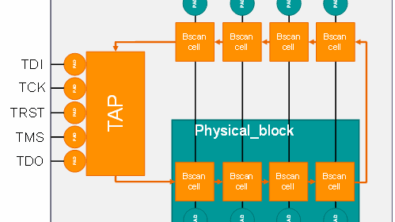

Boundary scan is an integral part of electronic circuit design, be it system level, PCB level, chip level or physical block level. This enables chip testing and debugging without using expensive test fixtures. The main idea here is to insert special registers or scan cells at the periphery of the circuit under test hence, the name boundary scan. These registers can observe data and provide test stimulus to the circuit. A serial interface, TAP, is used to have full control of the I/O pins at the boundary of the circuit under test.

Tessent Boundary Scan provides complete solution for automated generation and integration of on-chip test infrastructure, boundary scan, and test access port. It automatically generates and integrates RTL code for the TAP controller and boundary scan cells into the design RTL. Generates scripts for logic synthesis, simulation testbenches and test patterns for manufacturing test. Additionally, it supports generation of a pin order file which provides the package-pin data along with the boundary-scan chain sequence of the design and a BSDL file which provides a description of the way in which boundary-scan architecture is implemented in the design, along with many other collateral files.

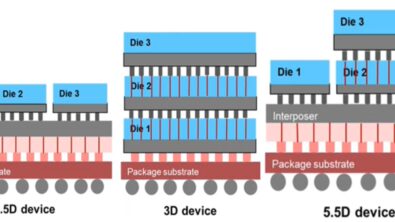

Many designs these days are hierarchical based. Can we implement boundary scan in hierarchical designs ?

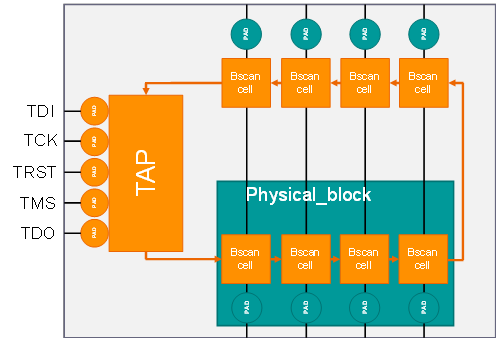

In some designs, there might be a need to place chip I/O cells directly into cores to be closer to the logic that they service. In such cases, the pad IO cells must be placed inside a module which is either a sub-block or a physical region. This technique is termed as embedded boundary scan (EBSCAN) and this provides significant physical design benefits, including simplified signal routing and improved timing. Tessent platform fully supports embedded BSCAN flow, this is used to insert BSCAN cells for the pad IOs which are present inside a module as shown in this figure. Tessent EBSCAN flow also automates integration of the boundary scan cells and verification of the resulting boundary scan segment within the core.

Figure 1. BSCAN implemented at chip top and physical block level

The webinar “Unlocking DFT success with Tessent Boundary scan” covers the fundamentals of BSCAN and EBSCAN DFT flow. The prerequisites, input files, DFT flow and output files generated are all discussed in great details. Lastly, the testcase attached in the webinar can be used to understand both the boundary scan DFT flow at the chip top level and at lower physical block level.

If you are looking for more information on BSCAN, EBSCAN, custom BSCAN cells, custom TAP implementation, integrating third party IP with BSCAN or defining Custom Boundary Scan Connectivity etc, please refer to Tessent Boundary scan User’s Manual.