How to boost reliability with early-stage reliability checks

By Chun-hsiang Chang

The rapid expansion of AI-powered consumer electronics is pushing IC manufacturing to the sub-2 nm frontier. To meet ever-stricter power and performance demands, design teams are re-thinking traditional methodologies. In this blog, we explore the benefits of early-stage reliability checks—enabled by Siemens Calibre Insight Analyzer — and how they help streamline complex IC design flows, reduce risk and boost product reliability.

IC complexity, power management and the scale of the challenge

Modern mobile devices aren’t just smaller—they’re smarter, packed with AI features that place heavy demands on power management. As designs incorporate multiple power domains and advanced leakage mitigation, the risk of subtle design errors increases. Traditional design methodologies, built around schematic simulation and layout extraction, struggle with these new complexities:

- Multiple power domains make simulation coverage challenging. Mistakes discovered late can require repeated, time-consuming reruns.

- Compressed development cycles leave little room for error.

- Schematic-only approaches often miss scenarios like domain leakage or floating gates due to less accuracy simulation setup for top-level schematic.

Early-stage, automated reliability checks are vital to identify power domain and leakage problems—before they become schedule-breaking issues.

Related: Solving inter-domain leakage challenges: Enhancing IC design with Insight Analyzer

Early-stage reliability checks: catching problems during schematic integration

When working at the top-level schematic integration phase, missing even small reliability issues can have big downstream effects. Classic examples include:

- Level shifters missing between voltage domains, causing domain leakage

- Floating gates, which introduce parasitic leakage in certain operating modes, missing simulation scenarios

- Power connection gaps that lead to unpredictable behavior

Often, traditional schematic simulation is not accurate or comprehensive enough to uncover these mistakes, especially as designs get more tightly integrated. The consequences are seen in cost, time-to-market and design reliability.

Related: Ensure power domain compatibility by finding missing level shifters with Insight Analyzer

Why pre-simulation checks matter

Pre-simulation reliability checking—before committing to full layout or extraction—offers designers a powerful early-warning system. Using a solution like Calibre Insight Analyzer, teams can scan their top-level schematics to surface common (but potentially catastrophic) issues like missing level shifters between power domains, unintended domain leakage paths, unconnected or floating gates and nets and power supply connection issues across interfaces.

Not only does this process improve coverage, but it enables “fail fast, fix early”—critical when deadlines are tight and design complexity is rising.

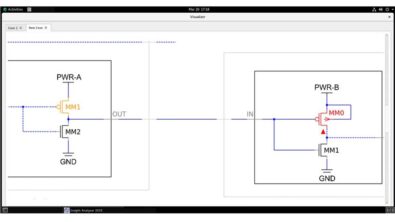

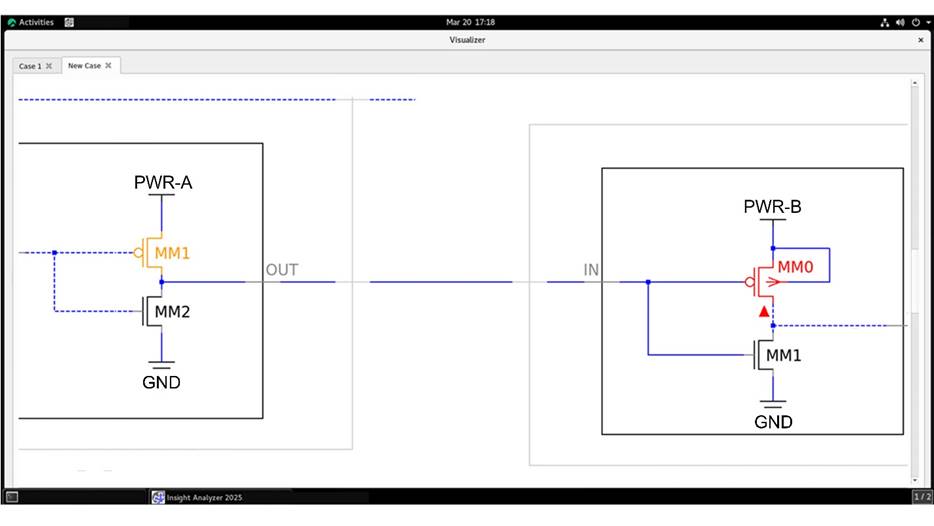

Cutting-edge verification: Insight Analyzer’s gray boxing and interface checks

Let’s look at how Insight Analyzer makes advanced reliability checking practical and efficient.

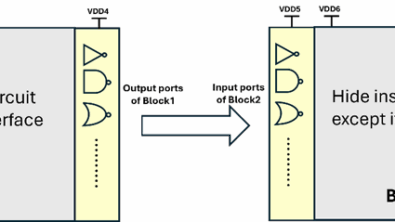

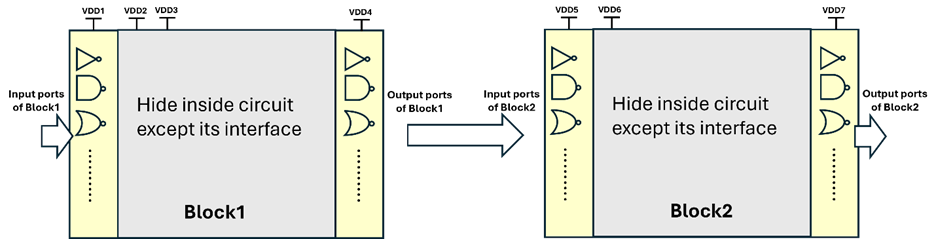

The gray boxing approach

Insight Analyzer’s “gray boxing” feature is pivotal during early top-level schematic integration. Here’s how it works:

- Designers define blocks in the schematic and “gray box” those sections

- Interface information between blocks is preserved and scrutinized

- Connectivity and reliability issues at block boundaries (like missing level shifters or domain mismatches) are flagged immediately

Crucially, this method does not require the entire circuit to be fully implemented before checks can begin—designers can iteratively fix and waive violations, enabling an optimized workflow.

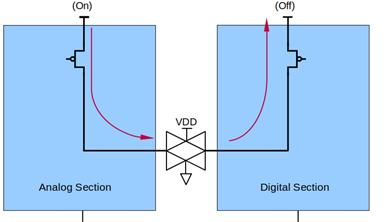

Interface verification for analog and digital

Whether your IC project is analog mixed-signal or digital (think memory or multiprocessors), interface checks are essential. The Insight Analyzer engine recognizes both analog and digital circuits in its comprehensive database, so teams catch:

- Digital domain crossings missing level shifting (also suitable for analog)

- Analog block boundaries with floating or improperly connected gates (also suitable for digital)

- Domain-leakage risk at block connections

Gray boxing and automated interface checks help uncover hard-to-detect reliability risks—dramatically reducing the chance of costly late-stage errors.

Faster design closure: from months to hours

Perhaps the most dramatic benefit of pre-simulation checking is cycle time reduction. Traditional reliability verification (using schematic simulation and electrical rule checking, ERC) for a large CPU can take months. With Insight Analyzer, the same reliability checks are completed in less than an hour. This improvement is made possible by the combination of shift-left pre-simulation coverage of likely risk scenarios, automated debug and violation reporting in the GUI and support for large schematics (including memory, multiprocessor and analog mixed-signal designs).

With development windows closing and mask costs rising, every hour saved counts. Automated, early reliability checks drastically shorten verification time, improving both project predictability and competitiveness.

Practical benefits of early-stage reliability checks

The benefits of early-stage reliability checks using Insight Analyzer are clear and proven in real-world designs:

- Cost reduction—detecting issues early costs at least 10x less than finding them during testing.

- Faster time-to-market—fast reliability analysis, fewer design iterations, streamlines approval process all contribute to meeting design timelines.

- Enhance design reliability—systematic identification of reliability risks, early optimization and better understanding of design margins leads to higher design reliability.

Conclusion

The move to smaller technology nodes and advanced AI-optimized SoCs is raising the stakes for IC designers everywhere. Early-stage reliability checking, made practical with tools like Calibre Insight Analyzer, is the key to meeting schedule pressures, power targets and silicon yield requirements.

Take the next step: resources for further reading!

Technical paper: Optimizing IC design flow through early-stage reliability checks

Product page: Calibre Insight Analyzer

Blog: Transforming pre-layout IC reliability analysis with Siemens Insight Analyzer