Physical design engineers…Learn the secret to generating signoff fill in P&R and accelerating your tapeouts

By Srinivas Velivala

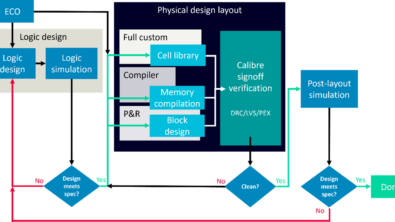

Place and route (P&R) engineers are always on the lookout for ways to optimize their design flows to ensure designs meet their design power, performance, and area (PPA) goals. The design rule checking (DRC) and fill flows are necessary steps on the way to tapeout, but the designers’ main focus is meeting those PPA goals while minimizing the time they spend fixing any problems in the layout. Unfortunately, the increasing complexity of design rules at advanced process nodes typically requires more time, not less, when closing these flows.

The first break in this logjam was the introduction of the Calibre® RealTime Digital interface, which made Calibre nmDRC™ and Calibre nmDRC Recon DRC verification available during the P&R process to help design teams find and eliminate critical design errors earlier in the design and verification flow. Getting systemic errors out of the layout during implementation resulted in significant time reductions in the overall flow.

Now, as part of our continuing innovation, the Calibre RealTime Digital interface offers P&R engineers the ability to add Calibre-optimized signoff fill during the P&R process. How does this help designers?

Glad you asked! Traditionally, engineers used the native fill solution of their P&R tool to generate fill during implementation, while running signoff fill solutions outside of P&R on bigger blocks and full-chip designs. However, as more and more companies move to advanced process nodes, there is an increased focus on reducing the number of variables that can impact those PPA metrics. One of these variables includes potential correlation issues between the P&R fill and the signoff fill, because fill mismatches can affect timing. To eliminate these types of time-consuming downstream problems, P&R engineers would prefer to use signoff fill solutions throughout their design flows. Now, they can.

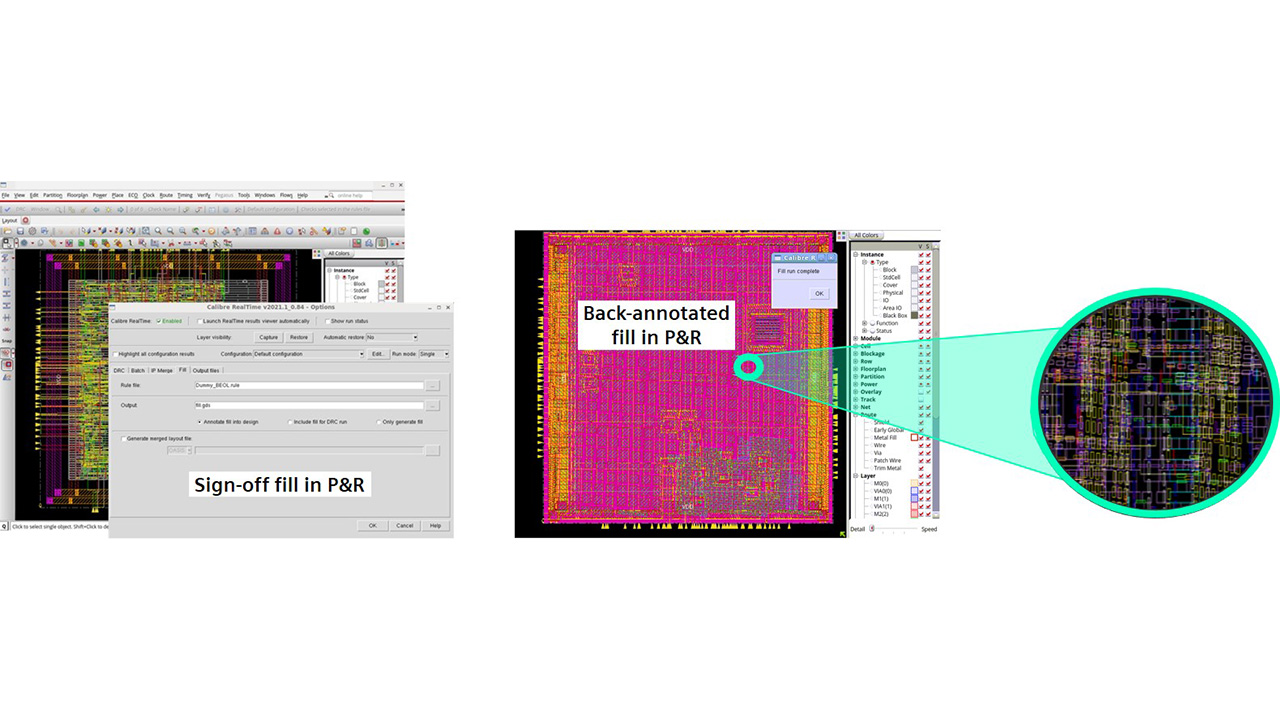

The Calibre RealTime Digital interface provides push-button access to the Calibre YieldEnhancer with SmartFill functionality in the P&R environment. Because the Calibre RealTime toolbar is integrated within all major design implementation tools, designers can seamlessly launch a Calibre YieldEnhancer signoff SmartFill run with a single mouse-click. Now they can pass the generated fill as input to downstream flows (such as timing and extraction), use the Calibre RealTime Digital interface to check the interaction of the design and fill shapes, and make quick edits to fix any DRC errors, all within the P&R environment. And, because both the Calibre DRC and fill solutions are proven signoff solutions, qualified at all major foundries, they can be confident in the results.

Multiple design teams in different semiconductor design companies have deployed the Calibre RealTime Digital fill solution across advanced nodes, ranging from 16 down to 4nm, with positive results. P&R engineers have validated the value of the flow—not only does it simplify generation of Calibre signoff fill throughout the P&R design flow, but they no longer have to worry about correlation or timing issues caused by mismatches between P&R and signoff fill solutions.

If you’d like to learn more about implementing signoff fill solutions during P&R with the Calibre Realtime Digital interface, download a copy of our paper, Implementing signoff metal fill in the P&R design environment for faster and more accurate tapeouts.