How place-and-route with intrinsic intelligence solves advanced node challenges

As SoCs become more complex, IC designers need the right automation tools to bring their designs to life. For digital implementation, the electronic design automation (EDA) software should master two things:

- Solve the technical problems to achieve the designer’s target goals

- Remove barriers to productivity by being easy to adopt and use

But too often, design teams are asked for power-user levels of expertise and effort when using their design tool just to achieve performance, power, area (PPA), and turn-around-time (TAT). Placing such a high demand on engineering resources can directly impact the cost, quality, and schedule of a project. It’s time for chip makers to demand better—a digital implementation tool that’s easy to adopt, easy to use, and achieves the best PPA and TAT.

Alpesh Kothari, the Chief Technologist for Aprisa, presented a detailed overview of the Aprisa intrinsic intelligent place-and-route solution at the Design Automation Conference (DAC), and the recording is now available as a webinar to view on demand.

In the webinar, Alpesh describes what makes Aprisa a unique tool for advanced node designs, and how its easy adoption, out-of-the-box best PPA recipes, and flexibility, makes it the right tool to fit into any digital flow.

What is Aprisa?

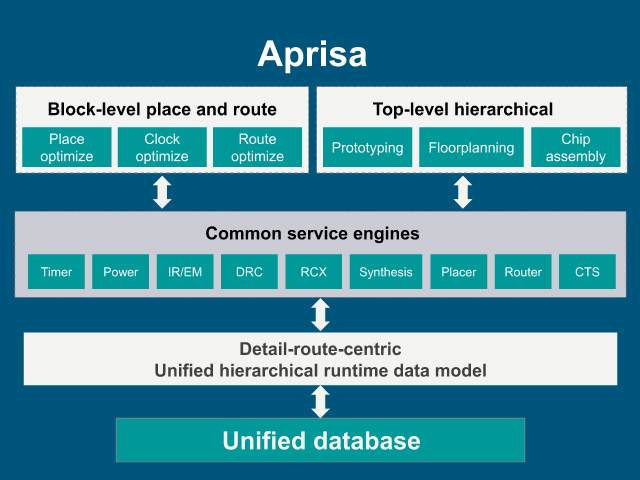

Aprisa is a complete RTL-to-GDSII design implementation solution. It includes both block-level place-and-route and top-level hierarchical design planning.

A unique feature of the Aprisa architecture is that it is detail-route-centric, which means the detail router gives guidance to all the other engines. This is important because at advanced nodes, the layers are uneven, the RCs are different, and therefore layer assignments, net topologies, and number of vias all have a big impact on the design results. Knowing this information starting at placement gives better correlation throughout the flow, and better correlation leads to fewer iterations, fewer ECOs, and faster tapeout.

What gives Aprisa intrinsic intelligence?

Intrinsic intelligence is the result of ~20 years of innovative software development that has gone into enabling Aprisa specifically for advanced nodes. Its single reference flow gives IC designers great out-of-the-box results and it can be reused in different blocks. One reference flow supports multiple blocks, across multiple technology nodes and multiple designs with very minimal changes to the recipe. The intrinsic intelligence of Aprisa allows it to work pretty much automatically, mostly skipping the need for placement regions, clock tree synthesis (CTS) guidance or R/C scaling. It’s all built in and tapeout proven.

Aprisa’s intrinsic intelligence allows our customers to lower their cost of ownership, reduce reliance on power users and custom recipe generation, scale engineering and CAD resources, and meet PPA faster than they thought possible. In the webinar, Alpesh describes the Aprisa reference script generator, which is how the designers generate their single flow scripts and achieve their metric targets with little customization.

Aprisa is certified on advanced process nodes at leading foundries including TSMC N5 and N4, and Samsung 4nm. Watch the webinar to see design implementation results with Aprisa, and the close correlation between Aprisa and the signoff tool and Aprisa and Calibre.

To learn more about Aprisa and how its intrinsic intelligent place and route flow enables the best possible tapeout time, lowest cost of ownership, and best PPA, watch the webinar!

Also available, customer webinars from Hailo, Arm, and IROC.