Bring your HPC design innovations to market faster with Aprisa

Designing integrated circuits (ICs) for high-performance computing (HPC) applications comes with serious challenges throughout the flow. Chip makers need to balance performance and power, meet tight design schedules, and manage engineering resources. The right digital implementation tools and methodologies can help solve the thorny issues in HPC designs, including placement and clock tree challenges.

You can learn more details, including real customer examples, when you download the new technical paper “Placement and CTS techniques for high-performance computing design.”

Placement and clock tree solution for HPC chips

Placement and clock tree synthesis are critical steps in the physical design of HPC chips, and they pose several challenges, including congestion, timing closure, power and thermal considerations, and design rule constraints.

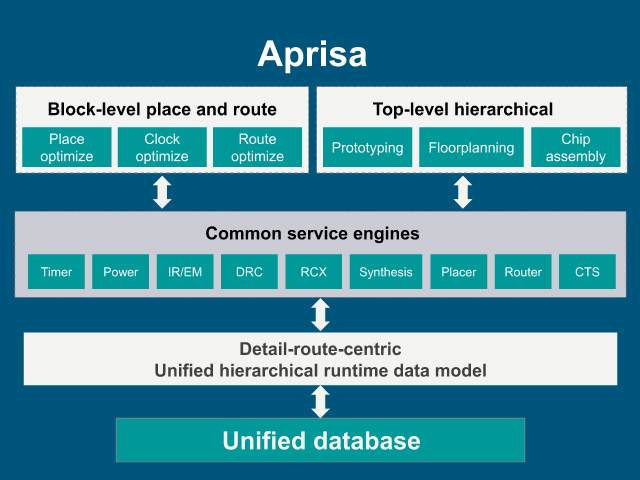

To address all the challenges of ICs for HPC applications, Siemens EDA offers Aprisa, a modern physical design implementation solution for hierarchical and block-level designs (Figure 1). Aprisa’s detail-route-centric architecture reduces the time to design closure with its unified data model, shared throughout the entire flow, bringing real route information and parasitics to any engine and any step in the place-and-route flow. This allows for consistent timing and DRCs across engines. Aprisa’s intrinsic intelligence ensures that designers will see excellent correlation with signoff tools and reduction on the number of ECOs.

The Aprisa architecture allows it to optimize placement with advanced knowledge of the detail routing, which minimizes the need for manual guidance from designers. In Aprisa, you can reduce or eliminate place guides altogether to quickly achieve optimal placement without having to rely on extensive engineering expertise and full-flow pre-runs. This early insight into timing, area, power, and congestion translates directly into saved time and cost, especially as design cycles increase due to the complexity and size of today’s ICs.

Make design tradeoffs with better analysis

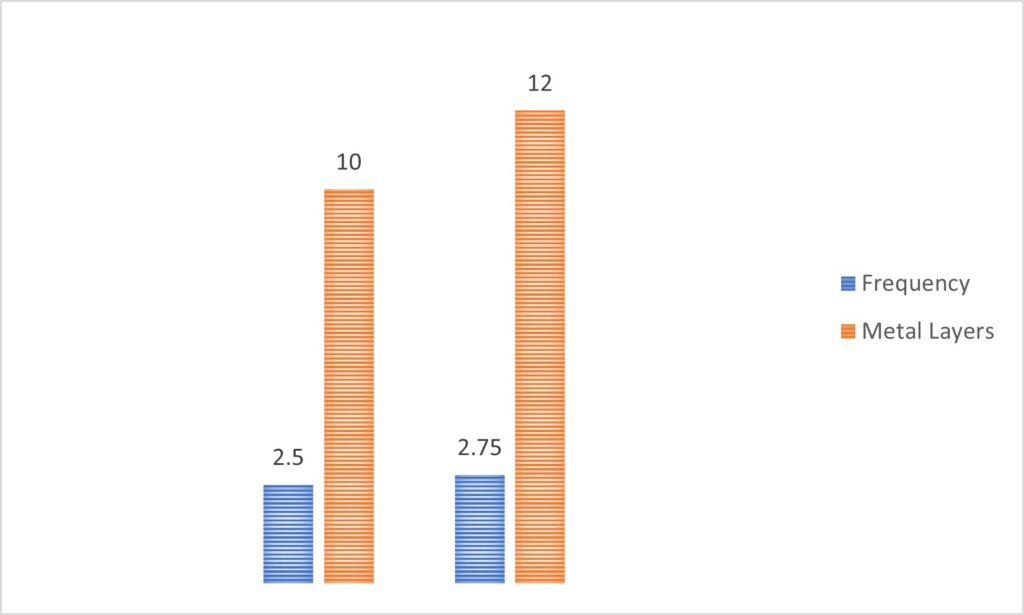

When designing on advanced nodes, you need to carefully weigh the benefits of saving power versus the added cost of additional metal layers. Each metal layer can increase the manufacturing costs dramatically, often exceeding millions of dollars.

With the early insight into the performance, power, and area (PPA) metrics you get with Aprisa, you can quickly assess the options for optimizing performance vs. power vs. cost very early in the flow. The opportunities to study metrics while keeping time-to-market goals, lets you make informed decisions about tradeoffs that impact the bottom line.

Clock trees for HPC chips

Clock tree synthesis (CTS), another top challenge in HPC designs, is a critical step in the physical design process, as it determines the final timing of the design. CTS involves routing the source of the clock to all the sinks, including registers, latches, clock gates and macro clock pins. Low-quality CTS can result in poor timing, high power consumption, and poor signal integrity.

The quality of CTS is impacted by three primary factors: clock skew, insertion delay, and buffering. Aprisa supports useful skew starting at placement and continuing all the way to route optimization, so that challenging frequency targets can be met. A strength of Aprisa’s CTS technology is that the push and pull offsets generated during placement optimization are realized during clock tree implementation.

Because Aprisa understands CTS starting at the placement optimization stage, it can produce the most optimal clock tree and reduce clock power.

During post CTS and route optimization, Aprisa will recover congestion created during CTS without impacting timing. With traditional tools, designers would have to iterate back to placement optimization to reduce congestion. Aprisa can also apply useful skew at later stages, to further improve the timing and achieve excellent correlation.

Conquering all the HPC design challenges

Aprisa addresses all implementation challenges for HPC designs at advanced nodes using easy to deploy out-of-the-box reference flows. Aprisa with intrinsic intelligence provides industry-leading correlation to signoff tools while providing technologies that reduce the number of ECO iterations. It ensures all PPA metrics are carefully balanced for HPC design implementation through high-quality clock trees, placement and patented routing technologies that reduce timing closure friction between the block and top-level during assembly.

With the help of the right place-and-route tool, you can bring your HPC design innovations to market faster with fewer engineering and compute resources.

Learn more in our white paper: Placement and CTS techniques for high-performance computing designs.