Watch Aprisa customer presentations from User2User 2023

At the 2023 User2User symposia in North America and European, real users shared their experiences with the Aprisa digital implementation software. The videos are now available on-demand.

Siemens’ digital implementation solution, Aprisa, was featured in presentations from users like Dolphin Design, Dream Chip, Maxlinear, and Arm, who describe how they used Aprisa to build better designs faster. These customer-led sessions showcase ease-of-use and great out-of-the-box results:

- “Timing closure of ultra low power design“ presented by Timothée Kocev, Physical Design Engineer at Dolphin Design

- “Reducing power and improving turnaround time” presented by Cas Groot, Director of SoC Engineering at Dream Chip

- “How to achieve optimal PPA at placement and carry it through to signoff” presented by Ravi Ranjan, Director of Physical Design at Maxlinear

- “Implementation of big infrastructure designs“ presented by Roma Rudra, Technical Director at Arm

Timing closure of ultra low power design, Dolphin Design

Dolphin Design is a provider of Semiconductor IP (including IP to enable Edge AI applications), Solutions Platforms, ASIC/SoC design and supply services. Timothée Kocev, Physical Design Engineer and member of the ASIC team at Dolphin Design in France, is in charge of integrating Aprisa into his company’s workflow. His emphasis in this presentation was reducing power consumption.

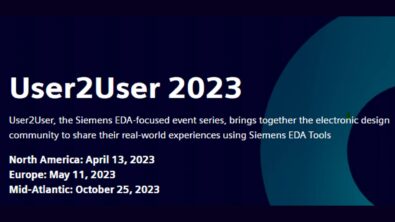

Timothée walks us through how they used Aprisa to solve challenges they faced on their recent project. Those challenges included the need for many timing scenarios as well as floorplanning and timing closure complexity.

Highlights:

- Aprisa was seamless to integrate and deploy into Dolphin’s existing flow.

- Aprisa delivered design closure with an automated flow and without user intervention.

- Aprisa achieved better leakage, better total power, and met performance targets, thus minimizing any ECOs.

- Aprisa showcased excellent correlation with signoff tools.

Watch this on-demand video to learn how Aprisa’s impressive AI-driven macro placement feature can save designers weeks of manual effort, while achieving power and performance metrics, with little to no designer intervention.

Reducing power and improving turnaround time, Dream Chip

Dream Chip is Germany’s largest independent engineering service provider focusing on the development and design of ASICs, SoCs, FPGAs, embedded software and discrete systems. In this presentation Cas Groot, Director of SoC Engineering, walks us through the benefits Aprisa demonstrated on their TSMC CLN12FFC designs, including:

- Best-in class PPA and fast turnaround time out-of-the-box, including minimal setup effort for CTS.

- Good quality of results due to Aprisa’s detail-route-centric approach that achieves excellent correlation pre- and post-route, giving Dream Chip designers early insights about congestion hotspots in a memory dominated design.

- Reduced power consumption without the need of endless ECOs that can be costly in terms of time-to-market.

Watch this on demand video to learn how your design teams can take advantage of Aprisa’s ease-of-use while achieving optimal PPA and fast TAT.

How to achieve optimal PPA at placement and carry it through to signoff, Maxlinear

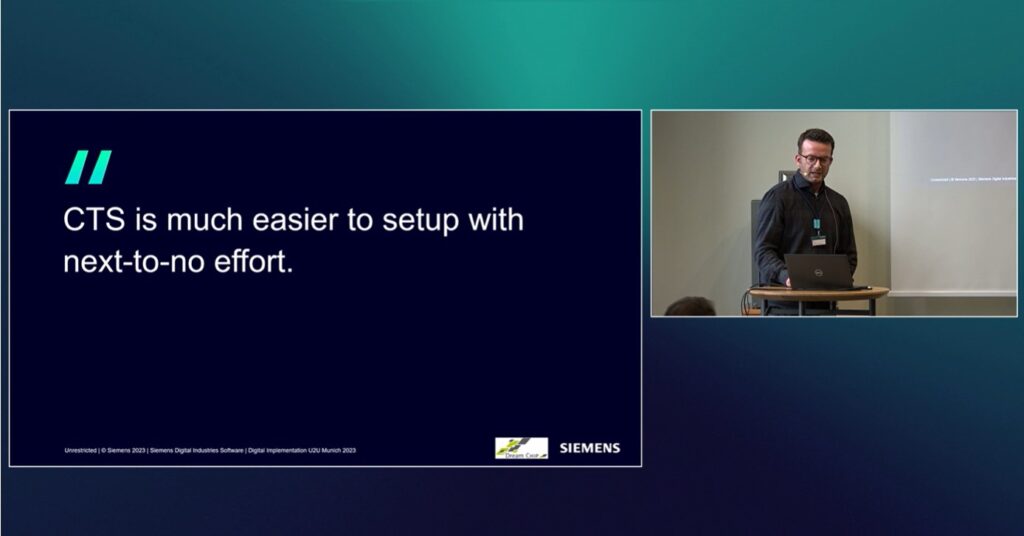

Maxlinear is a leading provider of radio frequency (RF), analog, digital, and mixed-signal integrated circuits for access and connectivity, wired and wireless infrastructure, and industrial and multimarket applications. Their products make multi-gig connectivity a reality through digital, high-performance analog and mixed-signal integrated circuits and software solutions. This session, presented by Maxlinear’s Director of Physical Design, Ravi Ranjan, covered their experience in the adoption of Aprisa for porting designs in 16 nm to the 5 nm technology. In Aprisa, Maxilinear found an easy-to-use flow with excellent correlation and integration to third-party extraction and STA tools.

More compelling for Maxlinear has been Aprisa’s salient features—its ability to maintain timing throughout the placement, CTS and post-route phases, all while achieving optimal performance, power, area (PPA). In addition, Maxlinear also values the fact that Aprisa does not require module place grouping, which eases the burden on their designers during the P&R flow.

You will learn how Maxlinear:

- Optimized and deployed their IC designs using Aprisa’s flow generator FlowGen.

- Reduced engineering expert time with Aprisa.

- Successfully deployed Aprisa in production for N16 projects.

- Was able to quickly enable Aprisa at N5.

- Accelerated productivity via Aprisa’s ease of adoption, flexibility, and reuse capabilities.

Aprisa has intrinsic intelligence resulting in a single reference flow, giving IC designers great out-of-the-box results. Aprisa can use one reference flow to support multiple blocks, projects and designs with very minimal additional guidance. Aprisa works with no-to-minimal need for placement groupings, clock tree synthesis (CTS) guidance, and R/C scaling. It’s foundry ready, and tapeout proven.

Watch this on-demand video to learn how Aprisa’s ease of use and intrinsic intelligence improve designer productivity and speed time-to-closure.

Implementation of big infrastructure designs, Arm

Arm silicon partners ship over 20 billion Arm-based chips every year, which are found in smartphones, computers, televisions, smart cars, wearable technology, and more recently servers. In this presentation, Roma Rudra, Technical Director at Arm, shared her team’s experience using Aprisa to implement a Compute Subsystem (CSS).

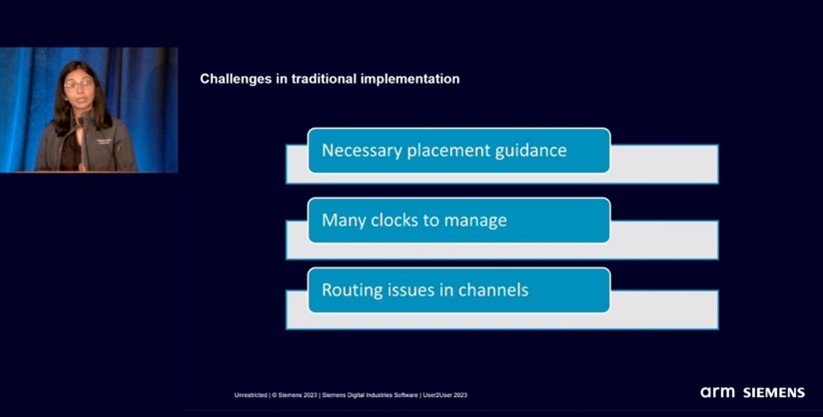

A CSS aims to deploy systems built around Arm IPs for the infrastructure market targeting Enterprise, HPC, Cloud and Edge servers. These are large to very large systems comprising of as many as 128 Arm cores in a monolithic die operating at >2.5GHz on leading process nodes. Roma described the approach and challenges to implement such large systems, and how Aprisa addressed those challenges through its tight correlation throughout the flow, and minimal need for guidance required to achieve optimal results.

Aprisa has a detail-route-centric architecture. That means that the routing information and parasitics are available to all engines throughout the flow. This is important because at advanced nodes, the layers are uneven, the RCs differ, and therefore the P&R tool needs to understand the layer assignments, net topologies and number of vias starting as early as placement. Knowing this information early gives better correlation throughout the flow, which leads to fewer iterations, fewer ECOs, and faster tapeouts.

Highlights:

- Aprisa implemented addressed the compute demand and power control challenges in a Neoverse core-based design.

- Aprisa’s detail route-centric architecture achieved superior correlation.

- Aprisa enabled DRCs to converge with minimal channel width.

- With Aprisa, no regions or placement guides were required to assist with placer versus competitive tools.

- Aprisa’s bring up was fast, easy for engineers to ramp up, and required minimal scripted guidance.

- Aprisa achieved a significant (33%) higher runtime performance.

The advantages of out-of-the-box tapeouts are that they lower the cost of tool ownership, reduce reliance on power users for custom recipe generation, allow better scale engineering and use of CAD resources, and meet optimal PPA for small and large designs at any nodes, faster and with fewer iterations.

Watch this on-demand video to learn more about how Aprisa achieves great correlation for even the largest and most complex designs.

Don’t miss these on-demand videos to learn how you and your team of designers can too, benefit from Aprisa’s superior correlation, ease-of-use and adoption and minimal guidance to achieve optimal PPA in a short TAT.