A cure for ECO headaches? Aprisa automates metal ECO

Engineering Change Order (ECO) is the process of inserting a small change in the logic, inside the gate-level netlist. ECOs are often required near the end of the design cycle to account for functional changes, bugs, timing changes, etc. As painful as the ECO cycles can be, it is better than the alternative option of a full design re-spin. The Siemens place-and-route solution, Aprisa, helps reduce the tapeout turnaround time (TAT) and mask re-spin costs by supporting metal-only ECOs with gate array cells.

Masks are getting more expensive with every node, a trend that seems to have no end. The cost can be managed by controlling the number of mask changes and by reducing design TAT. Both of these objectives are served by the two types of ECOs: base layer and metal layer. Base-layer ECO is where both the transistor level and the metal layers are changed by adding buffers, sizing cells, add combinational cells, etc.

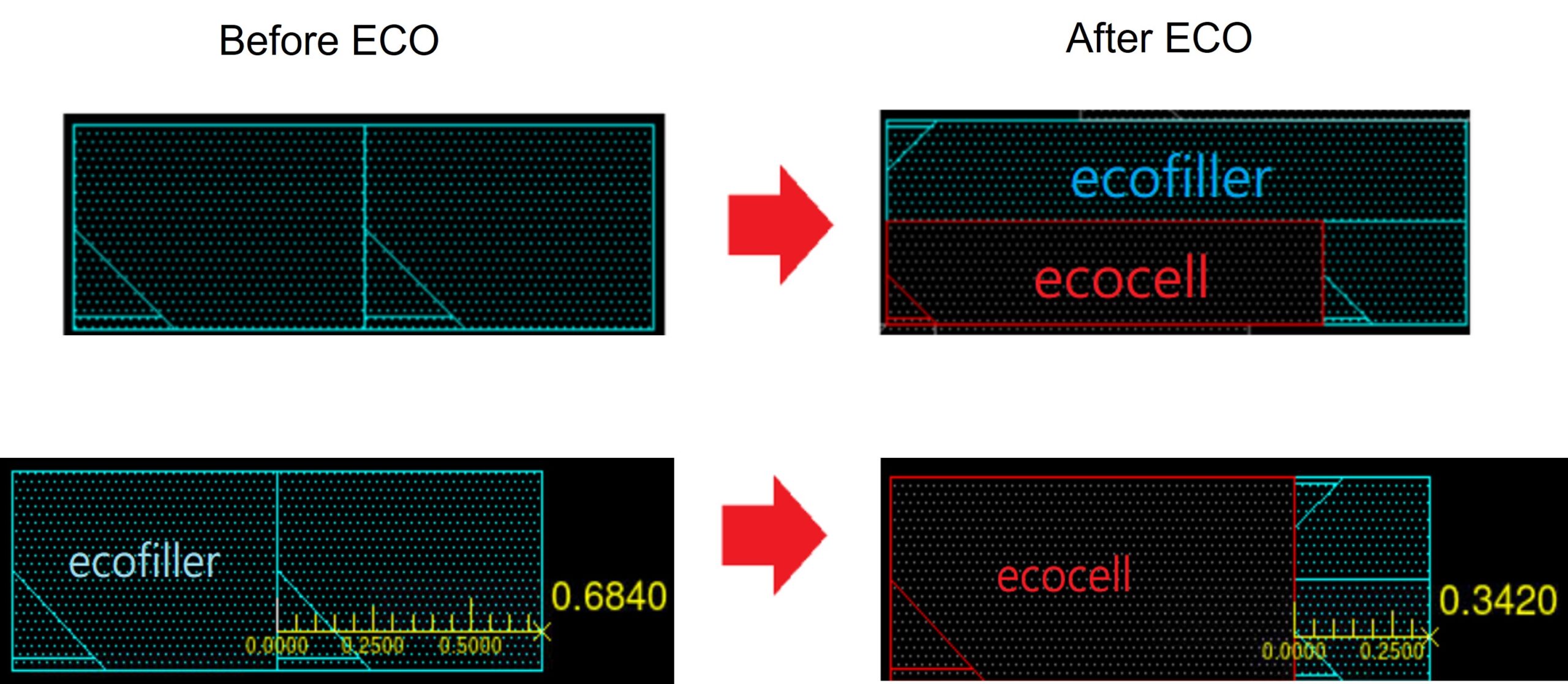

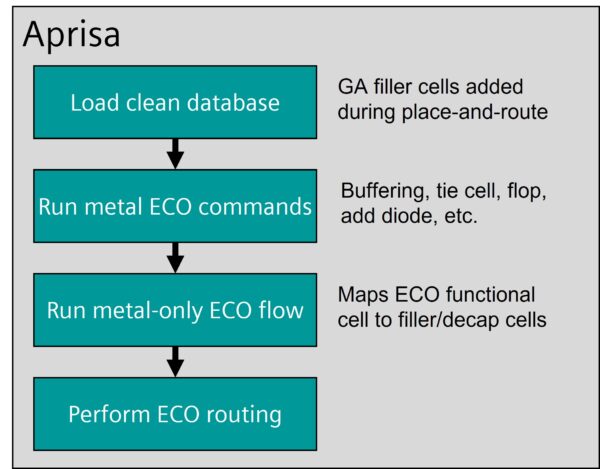

What we are more interested in for this blog is the case where the base layer is frozen and only the metal layers are permitted any changes. This metal-only ECO is achieved through a flow in which the fixes are applied only to the metal connections to make small design changes (Fig. 1).

The traditional ECO flow looks something like this:

- During the original synthesis and place-and-route, a number of spare cells are sprinkled throughout the design. Spare cells are sets of functional cells like buf, inv, nor, nand, mux, aoi, flop, etc. What and how many of these spare cells are used depends on the design.

- When an ECO is required, the designer checks what spare cells can be used to effect the change, then lets the place-and-route tool activate those cells by routing the necessary connections, and perform DRC and timing fixes.

This flow was adequate for older technologies but has limitations, including the limited functionality and drive-strength of spare cells, which can create DRC issues and makes timing closure tough, especially at advanced nodes, thus increasing TAT. Spare cells have one designated functionality, but a gate array can serve more functions and form different combinations of functional cells.

To control design and mask costs and meet tight tapeout schedules for complex, advanced node designs, designers often freeze design layers before they close timing/DRC completely. This introduces new challenges at various levels, including the library, the design, the methodology, and the EDA tools. One solution for ECO is to use gate-array cells instead of spare cells since gate-array cells provide more flexibility when it comes to late ECO changes.

Using gate-array cells

GA cells, provided by the library vendor, can implement any kind of functionality by making metal connections changes internally. These cells are known as GA filler cells, or mask programmable cells, or ECO filler cells. There are two types:

- GA filler/dcap cell, which can be converted to any functionality depending on its size

- ECO functional cells

For example, a filler/decap cell “Gfill1” can become ECO functional cells Ginv1, Gtie1, Gnr2d1; Gfill2 can be used as GBuf1, Gan2d1, etc.

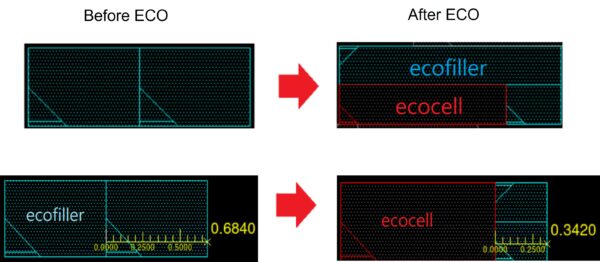

Performing the metal ECO flow with GA cells is similar to the traditional spare cell flow (Fig 2), except that the designer needs to use GA filler/dcap cells to fill empty gaps after place-and-route. The designer writes ECOs using ECO functional cells (Gbuf1, Ginv1, Gnd2D1 etc), where each functional cell will be replaced by one or more GA fillers by merging/demerging based on the size of it.

How Aprisa supports ECOs

Aprisa supports both base layer and metal ECO flows. Metal ECO maintains the FEOL/base clean layer using GA filler cells that are available in the library.

Aprisa offers a simple switch to apply metal ECOs. The process is easy and automatic. Aprisa checks the ECO mapping cells by looking at a cell’s GateArray property and then automatically maps the ECO functional cell to the corresponding GA filler cell. If a similar sized GA filler cell is not available, Aprisa can map to another size cell nearby and fill any gap with an ECO filler cell.

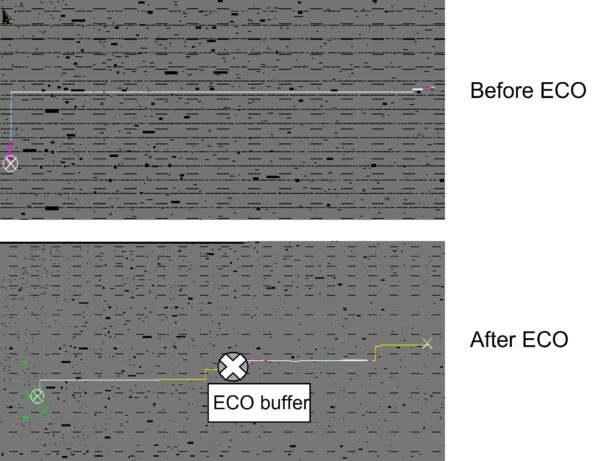

Aprisa addresses the challenge of ECOs causing additional timing or transition failures. This happens if an ECO happens in a region dense with logic cells or in an area where not enough filler cells are available. Traditional place-and-route tools can choose filler cells that are far away, requiring the long routing detours to connect the logic.

Aprisa offers a unique feature that keeps the GA cell search within a specified threshold. It will not perform the ECO changes if it would cause timing or transition issues. Because all steps of the Aprisa flow have access to detail-route information, this feature comes with no extra runtime penalty, performance degradation, or DRC violations.

Other features of the Aprisa metal ECO flow include support for single height and double height cell mapping. Aprisa can combine single-height GA filler cells to match a big ECO functional cell and split double-height cells into single-height cells and fill the gaps with smaller filler cells (Fig 3).

Implementing metal ECOs has always been a complex and tedious process. Many times, these ECOs are hand implemented by designers due to lack of support in the place-and-route tool. The entire ECO process is time consuming and often requires multiple iteration due to ECO rejections to achieve the desired outcome. Aprisa offers innovated, easy-to-use, and highly effective metal ECO capabilities to help designers reduce ECO cycles.

Aprisa helps reduce the tapeout TAT and mask re-spin costs by supporting metal-only ECOs with gate array cells in a way that is automatic and easy to deploy.

To learn more about the Aprisa place-and-route solutions, download our white paper, The Aprisa detail-route-centric solution.