Advanced analytics for accelerating RDC verification closure

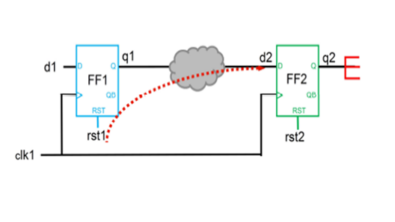

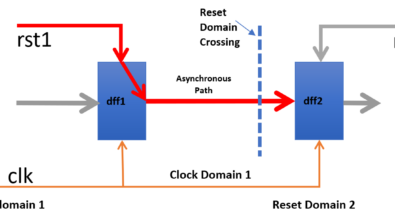

Complex reset mechanisms are embedded in advanced SoCs to meet low-power and high-performance requirements. Multiple reset domains in a design can cause reset domain crossing (RDC) issues when data from one asynchronous source reset domain propagates to either a different asynchronous, synchronous, or no-reset destination domain. It is essential to verify asynchronous data stability between different reset domains using various RDC static verification tools because data transfers between different asynchronous reset domains can lead to metastability issues and unpredictable behavior.

Challenges in analyzing RDC results

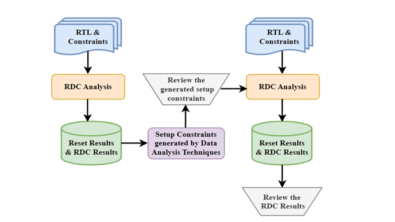

One of the significant challenges in ASIC verification is the sheer volume of data generated by RDC verification tools. This data must be carefully analyzed by design and verification engineers, requiring substantial effort and time. The large amount of data increases the risk of overlooking design bugs, which can result in costly silicon re-spins. Currently, RDC result analysis is performed manually, a process that involves multiple design iterations and is prone to errors. As newly written RTL designs typically lack initial setup constraints, an RDC analysis often reports numerous violations, necessitating considerable effort to identify root causes, apply constraints, and rerun the tools.

Streamlining RDC analysis with data techniques

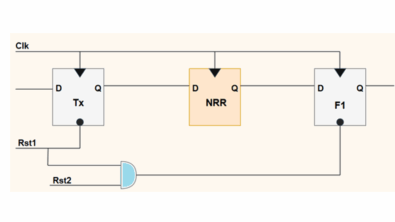

Many RDC paths result from common design or set up issues, such as asynchronous resets being incorrectly defined in different reset domains. By leveraging advanced data analysis techniques, we can identify these common issues by analyzing results, recognizing patterns, and suggesting set up-related constraints. These constraints help narrow down the RDC analysis results. By reducing the initial number of RDC violations, we allow verification engineers to focus on actual issues, leading to quicker verification closure and improved design quality.

Techniques for reducing RDC violations

Synchronous reset domains, directive specifications, reset ordering, stable signals, and isolation signals are critical in reducing RDC violations and streamlining the verification process. Grouping reset signals within a synchronous reset domain can prevent unnecessary RDC violations caused by asynchronous reset signals. Directive specifications help to avoid noise in the results by setting up constraints like clock-off conditions or pre-reset conditions. Ensuring that the receiver flop’s reset is asserted before the transmitter flop’s reset can prevent metastability from propagating through the design, thereby addressing common RDC violations that may arise from improper or missing reset ordering. Identifying stable signals that don’t pose a metastability risk and using isolation signals to block unwanted data transfers between different reset domains are essential strategies. These techniques ensure that only real RDC issues are flagged, minimizing false positives and leading to a more efficient and accurate verification process.

Conclusion

The manual verification of RDC results takes a lot of time and effort and there is a high probability that design bugs may be overlooked. Our proposed RDC verification solution of applying constraints suggested by advanced data analytic techniques is intended to reduce the manual set up and review effort, improve the quality of results, and avoid neglecting to specify constraints that lead to design bugs.

To learn more about how application of advanced data analytic techniques results in a major reduction of unsynchronized RDC crossings detected in a design. kindly download the full paper https://resources.sw.siemens.com/en-US/white-paper-reset-domain-crossing-design-verification-closure-using-advanced-data