No Reset? No Worries! Smarter Ways to Tackle RDCs to NRRs

As system-on-chip (SoC) designs continue to evolve, they’re not just expanding in size—they’re growing in complexity. Among the many challenges this evolution brings, one of the most subtle yet critical is the handling of resets. Modern architectures often juggle multiple asynchronous reset sources along with sequential elements, such as non-resettable registers (NRRs), which operate without dedicated reset pins. When a signal crosses from an asynchronous reset domain into an NRR within the same clock domain, it creates what’s known as a reset domain crossing (RDC). Why does this matter? Because if these crossings are not properly analyzed, the impact can be serious—ranging from metastability issues to functional correctness failures. This is where static RDC verification tools step in, helping ensure signals transition smoothly and safely across reset domains.

Where Traditional Tools Fall Short

Conventional RDC static verification tools typically rely on safe fanout analysis to determine whether the fanout elements of an NRR are safe. In practice, this means checking if the fanouts are either unconnected, share the same reset domain as the source/transmitter (Tx), or follow an ordered reset relationship. Sounds solid, right? The problem is that real-world designs are rarely this simple. With complex combinational reset logic and overlapping reset domains, tools struggle and thereby report both safe and unsafe RDC paths without the necessary granularity to distinguish between them. In existing RDC analysis flows for NRRs, tools typically depend on global preferences—such as a fixed skip-depth value that defines how many NRRs can be skipped for the safe fanout analysis—to decide if a crossing is safe. While simple, this one-size-fits-all approach isn’t configurable for specific design boundaries. The result? Reports filled with excessive noise that make it harder for designers to focus on genuine issues.

A Smarter, More Flexible Approach

What’s needed is a more flexible and intelligent approach—one that allows skip-depth to be defined on a per-path basis. In addition, context-aware filtering is required to enable the static RDC verification process to automatically filter out safe RDCs to NRRs. By proactively analyzing reset assertion sequences, including those involving complex combinational reset logic, this approach can precisely identify safe crossings. The result? Fewer false positives, reduced verification noise, and a much lighter burden on design teams who can now focus on the issues that truly matter.

Path-Specific Skip-Depth Configuration for N Clock Cycle Stability

While global preferences, such as a fixed skip-depth value, may be useful in some cases, these global settings lack the flexibility to handle specific design boundaries or various combinations of Tx reset and Rx clock domains. To address this, a more granular approach is necessary, where the skip-depth can be configured on a per-path basis, taking into account the specific Tx reset and Rx clock for each crossing. This ensures that only crossings matching the defined context are treated as safe, significantly improving accuracy in the verification process.

Intelligent RDC Filtering Using RX Fanout Reset Dependency

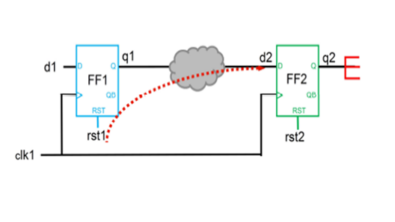

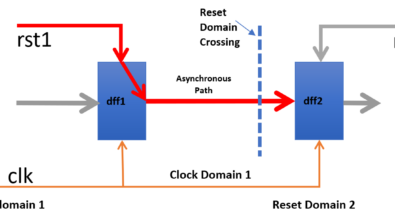

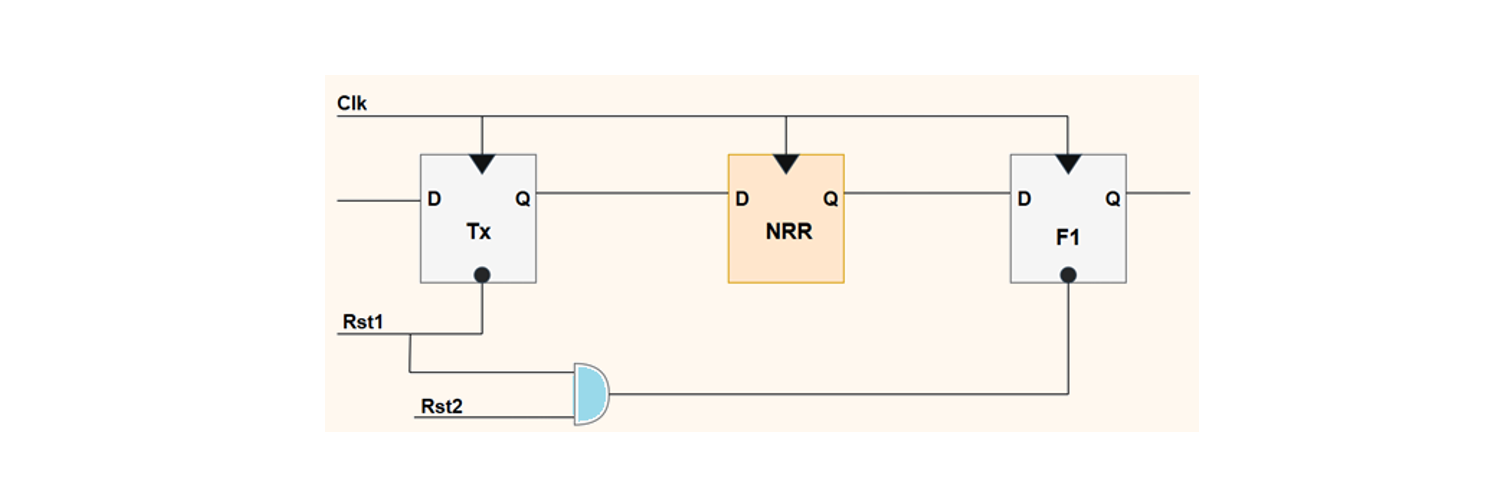

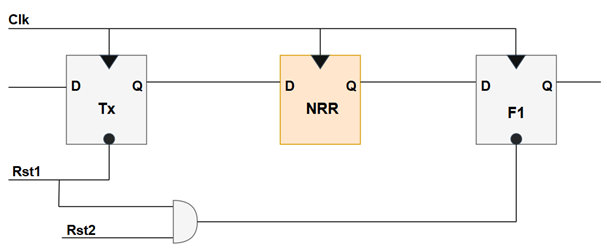

As reset architectures grow more complex, violations reported by tools can skyrocket, especially around NRRs — many of which are false positives. Consider the case illustrated in Figure 1, where multiple asynchronous reset signals interact within the same design segment. In this setup, register F1 is controlled by two independent resets, Rst1 and Rst2. The tools interpret the reset domains of Tx and F1 as distinct, so the RDC from flop Tx to flop NRR is considered to cause metastability and hence is considered an unsafe crossing.

When we walk through different reset sequences in this scenario, we observe that no metastability actually occurs. When Rst1 is asserted (low), it changes the state of F1 to a reset state regardless of the state of the other reset, thereby preventing any RDC issue. Additionally, when Rst1 is not asserted, Tx does not enter a reset state—meaning there’s no possibility of metastability at the Tx to NRR crossing. This example highlights how multiple reset dependencies and combinational reset logic can sometimes mislead static tools into flagging false RDC to NRR violations, making it essential to apply smarter analysis techniques that account for real reset behavior and suppress such non-critical crossings.

Wrapping Up

The integration of functional reset analysis into static RDC verification flows has proven to be a valuable enhancement for handling complex reset scenarios in modern SoC designs. By intelligently distinguishing between safe and unsafe crossings involving NRRs, this methodology significantly lightens the verification burden for design teams. Furthermore, the need for path-specific filtering, especially for crossings involving varied Tx reset and Rx clock combinations, highlights the limitations of relying solely on global skip-depth. Together, these innovations mark a substantial step forward in RDC verification, offering a smarter, more scalable approach for today’s increasingly intricate reset environments.

To learn more, kindly download the full paper No reset, no risk: Smart handling of reset domain crossings to non-resettable flip-flops.