Ensuring robust reset integrity in complex SoC designs through advanced reset tree checks

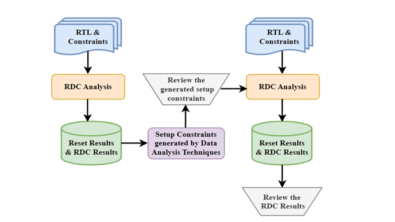

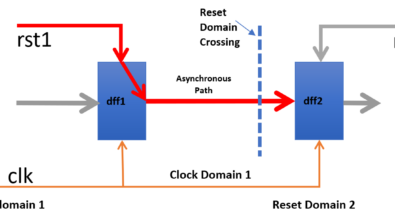

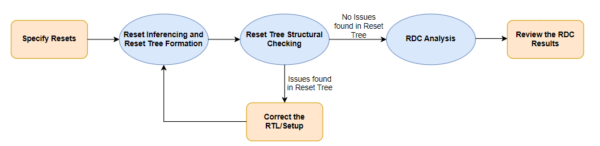

One of the foundational steps in the reset domain crossing (RDC) verification process is determining the structure of the reset tree within a system-on-chip (SoC) design. The reset tree is critical for tracking how reset signals propagate throughout the design, ensuring stable and predictable system operation. To construct this reset tree, engineers rely on static analysis techniques to examine the register transfer level (RTL) of the design and identify various reset signals. A complete reset tree structure allows designers to trace the flow of reset signals across the design and ensure that every sequential element is tagged correctly within its respective reset domain. By constructing this reset tree, engineers can more effectively manage any issues that may arise as resets propagate through the system, safeguarding the design from unforeseen failures.

Verifying the reset tree structure: Identifying issues early

Verifying the reset tree structure plays a critical role in catching potential issues early in the design process, long before the more complex RDC analysis begins. Early detection helps designers avoid timing issues and functional failures that could result from poorly managed reset signals. Basic checks in the reset tree verification process include verifying that a reset signal is not used as both synchronous and asynchronous reset or with dual polarity. It’s also important to ensure that signals designated as resets are actually functioning as reset signals, rather than serving other unintended purposes. Additionally, designers should check for registers that are controlled by overlapping set and reset signals, a scenario that can cause incorrect data sampling. Examining the reset path for the presence of latches, tri-state logic, or unwanted logic gates is also crucial, as these elements can introduce unexpected behaviour, including glitches or metastability. These basic structural checks form the backbone of reset tree verification, but they must often be supplemented with more advanced techniques to safeguard complex designs.

Advanced reset tree checks: Safeguarding against design failures

While basic checks are essential, modern SoC designs often face more complex reset-related challenges, necessitating advanced structural checks. One common issue arises when signals from different reset domains combine with reset signals before reaching a register. This can occur in low power designs utilizing reset signal gating through the Unified Power Format (UPF). When these combined signals originate from different reset domains, they can trigger RDC violations during analysis. Although static verification tools flag these violations to prevent potential metastability, they can also generate a significant number of false positives, overwhelming designers with alerts for crossings that are actually safe.

Another major challenge arises when non-resettable registers (NRRs) are used in asynchronous reset paths. While NRRs are a popular method for reducing power consumption, they can create metastability risks, as delays introduced by NRRs are often ignored by RDC tools. If the reset domain of the transmitter and receiver are incorrectly assumed to be the same, the potential for metastability increases, jeopardizing the reliability of the system. Similarly, some designs may unintentionally use reset signals as data, or vice versa, which can lead to incorrect data sampling and operational errors.

These structural issues, if left unresolved, can result in functional failures that remain undetected until later stages of verification, making them costly to fix and potentially requiring a re-spin of the silicon. For engineers working on cutting-edge SoC designs, detecting and addressing these advanced reset tree challenges early is essential to prevent major problems down the line. To address these complex reset tree issues, advanced verification tools like Questa® RDC offer specialized checks to catch potential metastability risks caused by NRRs, combined reset domains, or incorrect reset signal usage. Incorporating advanced structural checks into the RDC verification process not only ensures that designs are free from critical reset-related risks but also minimizes the time spent debugging and addressing false violations.

Conclusion: Strengthening SoC designs with advanced reset tree verification

The reset tree is a vital component in ensuring that modern SoC designs function reliably and efficiently. Basic verification checks lay the groundwork for detecting potential issues, but advanced reset tree checks are necessary to handle the complex interactions of reset signals in today’s sophisticated systems. By integrating the advanced checks early, design teams can significantly reduce the risk of costly issues arising later in the verification cycle, improving the overall reliability and stability of the system.

To learn more about advanced reset tree structural checks and how they can help manage the complexities of modern SoC designs, download our full whitepaper, Effective identification of reset tree bugs to mitigate RDC issues. The paper delves into advanced techniques for identifying complex reset tree errors before they escalate into major issues during RDC analysis. The paper also shares the results of a case study in which Questa RDC was run on three designs to identify reset tree errors that could escalate into serious design bugs.