Unlocking Performance: How Computational Storage Transforms Data Processing

Computational storage devices (CSD) represent a paradigm shift in how data processing and storage are handled in modern data centers, providing significant benefits for applications requiring large-scale data management and real-time analytics.

This blog discusses the performance characteristics of CSDs, contrasting them with traditional storage solutions while addressing the unique verification challenges they present. It highlights how Avery NVMe Verification IP ensures performance and reliability through compliance checks, stimuli generation, and system-level validation with virtual in-circuit simulation (VICS).

Computational Storage: Revolutionizing Data Processing

Computational storage integrates processing capabilities directly within storage devices, reducing the need to transfer data to the host CPU for processing. Key components include subsystem local memory (SLM)—a host-accessible, byte-addressable memory dedicated to compute namespaces—and compute namespaces, which store and execute computational programs independently of the host. Programs, whether downloaded or pre-installed, perform tasks like encryption and data analytics directly within the storage infrastructure, improving efficiency by minimizing data movement and enabling in-situ processing.

The execution of programs within compute namespaces requires initial set up, such as loading programs and creating memory ranges. These ranges define the specific parts of memory the compute namespace can access, ensuring targeted computation. Programs access data within SLM ranges and perform computations without transferring data outside the SSD. As a result, only the results may be sent back to the host, reducing bus traffic and latency, making computational storage highly efficient compared to traditional systems

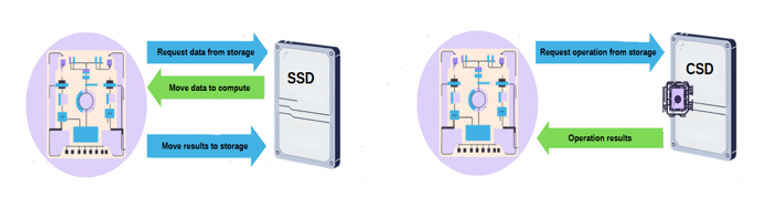

Traditional vs. Computational Storage Models

In traditional SSDs, data is read from the SSD to the host for processing, resulting in high data movement and increased latency. In contrast, CSDs minimize data transfers by allowing programs to execute directly within the compute namespace. This reduces latency and enhances bandwidth efficiency, thus enabling more responsive systems, especially in data-heavy environments.

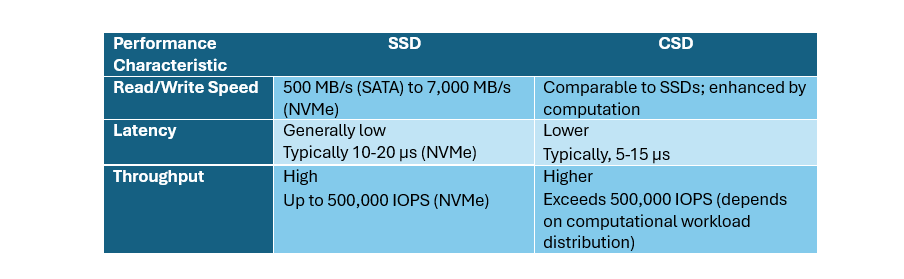

Performance characteristics comparison of SSDs and CSDs

CSDs offer notable advantages over traditional NVMe SSDs due to in-situ processing.The table below highlights how CSDs outperform traditional SSDs in key metrics like latency, throughput, and data movement efficiency.

Complexity in CSDs: Addressing Verification Hurdles

The integration of compute resources and SLM in CSDs introduces additional complexity into the NVMe architecture. Ensuring protocol compliance, accurate memory management, and seamless interaction between namespaces becomes more challenging. Detecting protocol violations and unexpected behaviours early in the design process is critical to ensure the smooth operation of CSDs.

Verification also needs to account for various edge cases, fault conditions, and corner cases that might arise during computational tasks, making robust testing essential. Moreover, as CSDs handle computational and normal SSD operations simultaneously, ensuring that they perform consistently under different workloads becomes a verification challenge

Avery VIP for NVMe: Ensuring Robust Validation for CSDs

To address these issues, Avery NVMe Verification IP provides a robust suite of tools designed for thorough validation. It includes an embedded monitor for protocol compliance, utilizing a shadow NVM storage model for data score boarding and a suite of over 1,800 checks. Additionally, the tool offers comprehensive stimuli generation capabilities, covering a wide range of scenarios—from normal operations to corner cases—through features like a transport-independent stimulus library, error injection, and automation via APIs.

Avery NVMe Verification IP also equips users with essential logging and debugging tools, such as a transaction logger for command traceability and a beat logger for anomaly analysis. Coverage metrics are employed to ensure comprehensive validation, utilizing functional, code, and cross-coverage metrics to identify gaps in testing.

Questa Verification IQ (VIQ) enhances this process with advanced analytics and visualization tools for real-time tracking and regression analysis. Performance assessment features track key metrics like latency, throughput, and input/output operations per second (IOPS), providing insights into operational efficiency and helping to identify potential bottlenecks, ultimately improving the reliability and performance of CSDs.

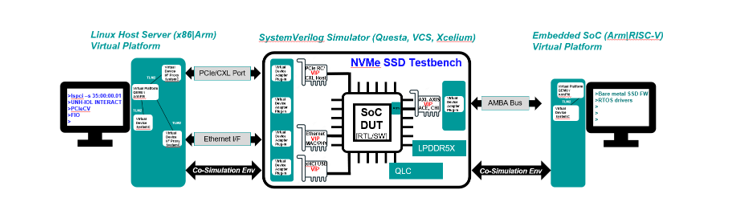

VICS: Enabling Comprehensive System-Level Co-Simulation

To overcome the challenges associated with system-level verification before expensive tape-outs, Avery NVMe Verification IP introduces a robust approach that integrates system-level co-simulation of host-based and embedded software with SoC hardware RTL. Virtual in-circuit simulation (VICS) employs software-driven verification techniques, utilizing standards compliance and integrated benchmarking tools, such as PCIe-CV and FIO, to provide flexible simulation environments and full debugging capabilities. System-level co-simulation with VICS allows early detection of issues by simulating real-world interactions between host software, embedded software, and hardware components. It reduces the risk of silicon failures and improves the confidence level in product robustness when submitted for NVMe integrator’s list requirements.

Verification: The Gateway to CSD Excellence

CSDs are transforming data processing by integrating computational capabilities within storage systems, enhancing efficiency and reducing latency. By minimizing data movement, CSDs enable faster and more responsive operations compared to traditional storage architectures. However, this complexity introduces significant verification challenges.

Avery NVMe Verification IP effectively addresses these challenges with a robust suite of tools that ensure protocol compliance, effective memory management, and smooth interactions between compute namespaces. With features like comprehensive stimuli generation, advanced logging and debugging, and system-level validation through VICS, Avery NVMe Verification IP guarantees reliable performance under diverse workloads. As organizations adopt CSDs, effective verification will be key to unlocking their full potential in modern data management.

For more information on effective verification strategies for computational storage design, download our new whitepaper Accelerating verification of computational storage designs using Avery NVMe Verification IP.