Leveraging BIST to reduce silicon cost in ISO26262 compliant semiconductors

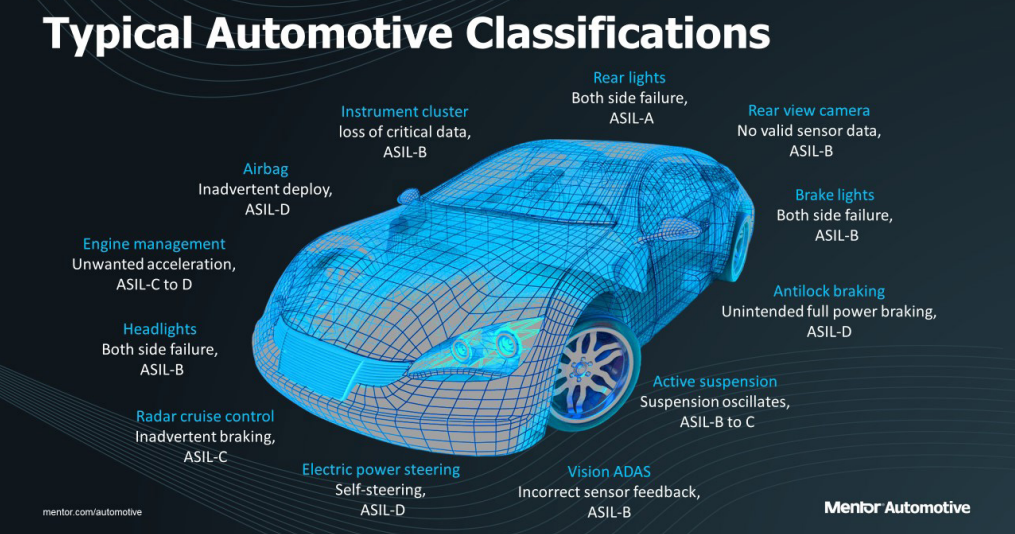

IC complexity for automotive applications continues to grow with experts estimating that automotive electronics will eventually exceed 50% of total vehicle cost. This growth is primarily driven by the migration to EV, ADAS and AV systems.

In addition to providing these next generation features, IC manufacturers must implement sufficient safety components to mitigate failures, and achieve the desired Automotive Safety Integrity Level (ASIL).

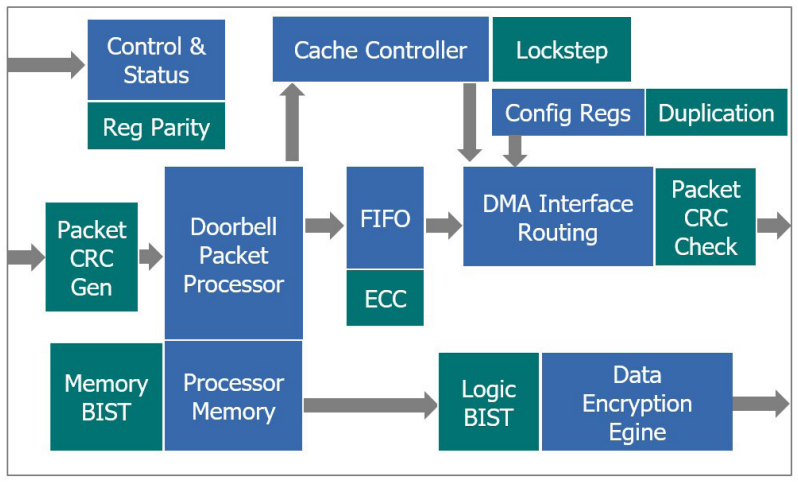

Unfortunately, safety isn’t free and often requires additional silicon resources to ensure the product fails safely. A safety architecture is often comprised of dedicated hardware safety mechanisms, software safety, and manufacturing test technologies. The diagram below shows an example hardware safety architecture, and each safety mechanism deployed has their unique impact on power, performance, area, and safety.

Manufacturing test technologies, commonly known as DFT (Design for Test), is one area garnering much attention. The traditional use mode for DFT is to identify post manufacturing defects. With enhanced in-system test capabilities, project teams are leveraging already present DFT hardware to identify run-time failures, saving the need to add additional dedicated safety hardware. Ultimately, complementing hardware safety mechanisms by leveraging DFT hardware to detect run-time failures will help reduce the power, performance, and area impact incurred when adding dedicated hardware.

If you are interested in learning more, a white paper is available describing the methodology and tradeoffs: “USING BUILT-IN-SELF-TEST HARDWARE TO SATISFY ISO 26262 SAFETY REQUIREMENTS”