Dawn of the new Mixed-Signal Verification Era and the need for revolutionary AMS Verification solution

I have been following and attending leading industry events focused on Semiconductor industry such as Hot Chips & MWC and invariably see 2 key trends driving the semi industry growth. This year’s Hot Chips, a leading conferences on high-performance microprocessors and related integrated circuits, hosted 25 talks, 16 of them focused at least in part on chips handling artificial intelligence jobs and rest on handling 5G applications. The same trend appeared in Mobile world congress in Barcelona where we saw 5G chips and custom hardware focused on artificial intelligence applications. These AI and 5G papers and applications spanned a broad range from ultra-low-power devices for the Internet of Things and smartphones to power-hungry slabs of silicon for the data center. However, there is one theme common in each of these applications – complex analog mixed signal ICs and the need for better mixed-signal verification solutions.

For example, let’s look at one of the hot topics today – machine learning. Most machine learning and artificial intelligence processors today use the Von Neumann architecture. This has a memory to store the weights and data, and the CPU does all of the computation. The biggest bottleneck in this architecture is the data movement, especially off-chip, which causes a lot of penalty in energy and latency. There is an increasing demand for high-speed high bandwidth PHYs to address this movement of data. These PHYs are predominantly complex analog mixed signal circuits.

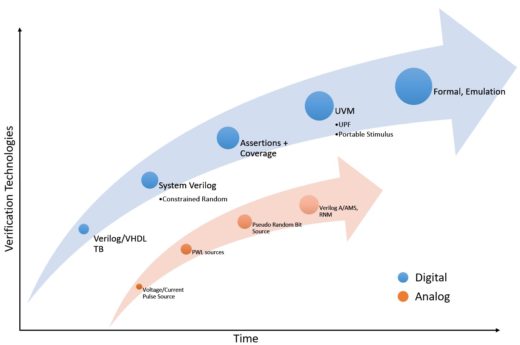

To verify these high speed/high bandwidth PHY requires a faster, high capacity mixed-signal simulator that doesn’t compromise on accuracy. To verify these complex mixed-signal PHY requires applying unique methodologies for top-level and each class of sub-design within an IC. In the pure digital verification space, the advent of new technologies, such as constrained-random data generation, assertion-based verification, coverage-driven verification, formal model checking, and intelligent testbench automation, have changed the way teams achieve functional verification productivity. However, most of these advances and new technologies have not been perfected for the analog domain and have not been extended to verify mixed-signal designs (Figure 1).

Figure 1: Digital versus Mixed-Signal verification methodologies progression

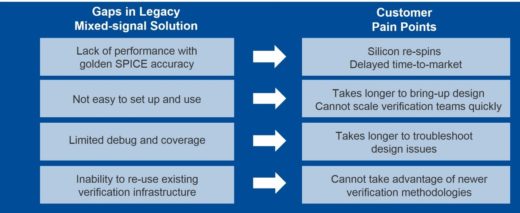

Further the existing mixed-signal solutions available were built based on the 20+ year old requirements and needs which does not apply to today’s mixed-signal designs. These gaps and pain points are illustrated in Figure 2 below.

Figure 2: Technology Gaps and Customer Pain points

At Mentor we are extensively investing in research and development of futuristic analog mixed signal verification technologies that can meet the requirements for today’s and future complex mixed-signal ICs.

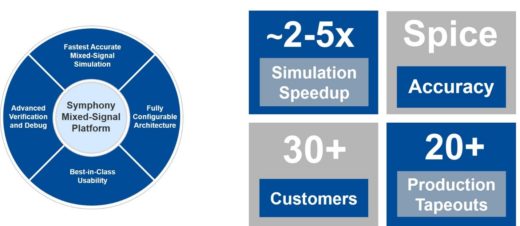

As a result of Mentor’s innovation, I am happy to announce Symphony, Mentor’s next-generation mixed signal verification platform.

I am excited to be a part of the Verification Horizons BLOG, and will be launching a new series of Analog Mixed Signal topics. Our goal is to have resourceful, informative and interactive blog posts about Analog Mixed Signal, from purely analog, mixed signal, RF to Real Number Modeling and verification techniques including ML based technologies from Solido product portfolio. Analog Mixed-Signal is a complex and evolving space, so let’s have fun with it!

Figure 3 : Introducing Symphony Mixed-Signal Platform

To further learn on Mentor’s executive vision of Symphony and how it addresses the next wave of mixed signal verification challenges you can view the video below from Ravi Subramanian – VP & GM for Mentor-Siemens IC Verification Solutions Business.

Ravi Subramanian – VP & GM ICVS Video