How Any Verification Engineer Can Quickly Create a Complex Testbench

Over the past decade or so, the state of the art in design verification has taken a huge leap forward to meet the challenge of comprehensively-verifying designs that are mind-numbingly complex. The goal, of course, was to achieve more-comprehensive verification without radically increasing the resources applied to the task. Constrained-random stimulus helped engineers several orders of magnitude more stimulus using automation. Commercial verification IP provided engineers more-efficient ways to interact with complex interface protocols. The UVM brought reuse methodology to verification environments, both in terms of reuse of infrastructure and in terms of knowledge. All of these things increased how much a verification team could accomplish.

Designs have continued to get more complex, and project cycles have continued to get shorter, and verification teams are now responsible for verifying even more. The key question, of course, is where to look to increase verification efficiency and achieve even more verification with the resources we have.

There are several recognized areas of inefficiency with the verification process being used today. The good news, though, is that automation can be applied to bring efficiency to all of these areas!

UVM Framework

Setting up the structure of a complex UVM environment requires the creation of a significant amount of “boilerplate” code. As a consequence, it can take days or weeks to create the structure of a UVM environment from scratch. This becomes a key bottleneck when a team is responsible for verifying multiple designs per year.

Mentor’s UVM Framework helps verification engineers quickly generate the framework a UVM testbench environment – whether simple or complex. The UVM Framework scripts quickly take care of setting up key testbench structure, that can later be customized by the verification engineer. The end result is a functional testbench in a couple of hours instead of a few days or weeks.

Questa VIP Configurator

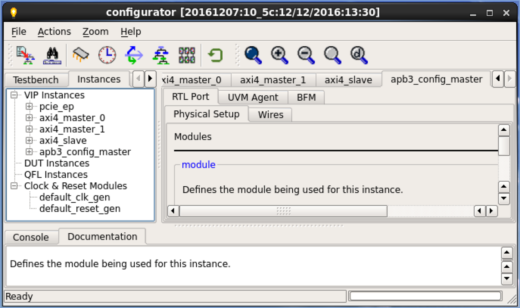

Verification IP insulates the verification engineer from understanding all the minutia of today’s complex interface protocols. However, today’s VIP is highly configurable to support all variants and use models of an interface protocol. Sifting through all the configuration options and selecting a proper and legal configuration is error prone and time consuming.

Questa VIP’s configurator steps the verification engineer through the process of selecting a proper configuration for a VIP. The output of the Questa VIP configurator integrates with the UVM Framework, such that the configured VIP is easily and automatically be stitched into the UVM environment. This, of course, saves the verification engineer time both in terms of selecting a proper configuration, and in terms of integrating the configured VIP into the testbench environment!

Questa inFact

Directed tests are, of course, known to suffer from low test-creation productivity, and from the limitations of the test writer to envision corner cases. Constrained-random tests definitely boosted stimulus-generation raw productivity and helped to generate hard-to-envision corner cases. However, they also suffer from generating redundant tests (“random” is right there in the name, of course), and from being difficult to steer. Furthermore, transaction-level constrained random really doesn’t scale well to generating comprehensive scenarios.

Questa inFact is a portable stimulus test tool that brings efficient and automated test generation to block, subsystem, and SoC-level verification environments. inFact allows a verification engineer to suppress redundant stimulus, and provides a high degree of control over focusing the generated stimulus. inFact enables extremely-efficient transaction-level verification, but also enables creation of comprehensive and reusable scenario-level tests. In both cases, enabling the verification engineer to accomplish more with the same resources.

Testbench Automation from Mentor Graphics

If you’re attending DVCon, come see our tutorial titled Testbench Automation : How to Create a Complex Testbench in a Couple of Hours. Also, be sure to stop by the Mentor Graphics booth! We’d love to talk with you about how you too can boost your verification productivity and verify more with the same resources!

Comments

Leave a Reply

You must be logged in to post a comment.

The goal shouldn’t be to create a “complex” testbench, but a full featured one that is as simple as possible.