Modeling CPU Instruction Sets with a Portable Stimulus Specification

Portable Stimulus Specification tends to bring to mind applications where a given verification scenario needs to be reused across multiple verification engines, such as simulation, emulation, and post-silicon, or must be reused between block-level verification and SoC-level verification. These are, of course, key application areas for the Portable Stimulus Specification being developed by the Accellera Portable Stimulus Working Group (PSWG). But applications for a Portable Stimulus Specification go far beyond just applications where verification portability is critical.

In the latest issue of Verification Horizons, Staffan Berg and Mike Andrews write about using the graph-based Portable Stimulus Specification used by the Questa inFact tool to model instruction sets.

What’s Unique about Instruction Sets?

Modeling an instruction set in order to generate instruction streams poses some unique challenges compared to generated transaction-oriented stimulus.

First off, instruction sets use distinct, but overlapping, fields to describe the attributes of the different instruction formats. Depending on the instruction format, different fields are significant. This is very different from transaction-oriented stimulus, where all transaction attributes are always significant. In addition to presenting a modeling challenge, having all these duplicate data fields presents a performance challenge for constraint solvers.

The state space of instruction sets is also enormous. This makes modeling coverage goals challenging, and reaching those coverage goals even more challenging!

How does a Portable Stimulus Specification Help?

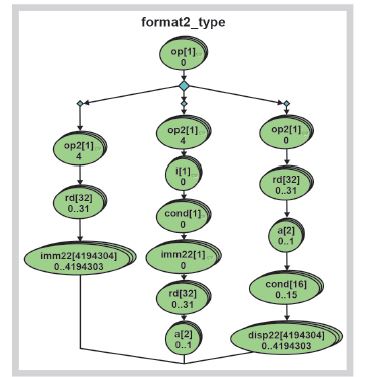

A graph-based portable stimulus model allows the model writer to capture the natural structure of the instruction set, and only deal with the fields of interest for each instruction format. In the screenshot below, you can see how each format-specific branch of a graph contains the opcode fields of interest and only those.

In addition to making modeling simpler, this helps with tool performance, since the tool knows which opcode fields are actually significant and which are irrelevant for a given instruction type.

A graph-based Portable Stimulus Specification is an object-oriented description, which makes reuse by inheritance and reuse easy! This makes it easy to chain together multiple instructions and capture cross-instruction constraints to model useful corner cases that arise from implementation details, such as pipelines.

So, if you’re interested in how a Portable Stimulus Specification can be applied to make instruction-stream generation simpler, have a look at the article A New Stimulus Model for CPU Instruction Sets in the latest issue of Verification Horizons.

https://www.mentor.com/products/fv/verificationhorizons/

If you’re interested in learning more about Questa inFact, the graph-based portable stimulus tool from Mentor Graphics, please watch New School Stimulus Generation Techniques:

https://verificationacademy.com/seminars/New-School-Stimulus-Generation-Techniques