Video: Leveraging the RISC-V efficient trace (E-Trace) standard

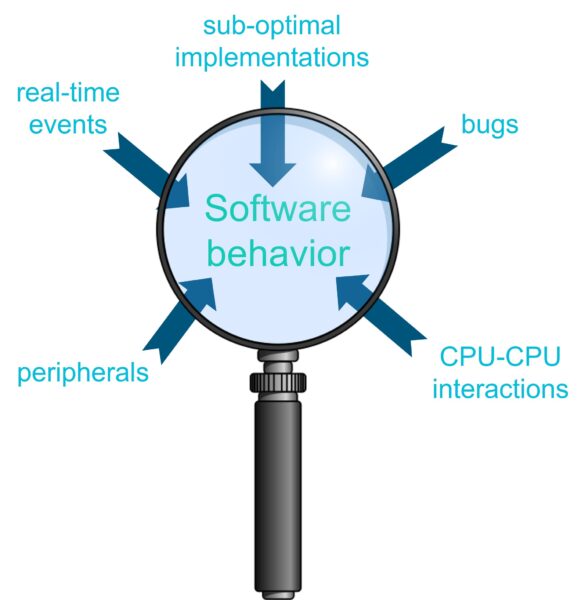

Understanding program behavior in complex systems is not easy. Understanding the behavior of complete systems is even more challenging. Get non-intrusive, full-speed and system-level visibility with E-Trace.

Processor trace gives developers access to critical insights and forensic capabilities to manage the risk of building embedded systems. Efficient Trace for RISC-V (E-Trace) was the topic of a well-attended presentation at the RISC-V Summit held on November 7-8 in Santa Clara, CA. Iain Roberston, Senior Director of hardware engineering in the Tessent group at Siemens EDA delivered “Leveraging the RISC-V efficient trace (E-Trace) standard.” His 17-minute presentation was recorded and is now available on-demand.

What you’ll learn:

- Trace basics, including ways in which trace is commonly implemented

- An overview of the RISC-V Efficient trace (E-Trace) standard

- How processor trace is used to improve embedded software and applications, including a case study of how Seagate used E-Trace

- Comparisons of different E-Trace solutions

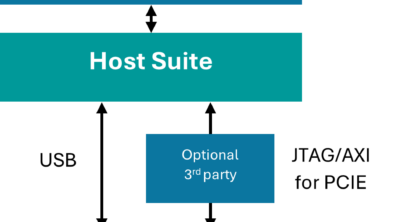

Processor trace is a common non-intrusive debugging technique which many development teams and customers expect as a minimum feature of any SoC deliverable. Trace captures, encodes and transmits off-chip a record of executed processor instructions, which software tools can use to reconstruct the exact execution sequence of a program. Embedded developers can then inspect the execution sequence to verify the RISC-V instruction set architecture (ISA), debug application code, profile the processor and explore code coverage.

Representatives from Siemens led the RISC-V Debug and Trace Working Group and donated the trace algorithm to the RISC-V International community. Siemens now offers the market-leading RISC-V trace solution, The Tessent Enhanced Trace Encoder. Learn more about Tessen’t RISC-V solutions.