Test technologies enabling AI

At the Silicon Valley DFT and Test Conference in Santa Clara, CA on October 23, the tight-knit community of DFT and test engineers gathered to share knowledge and solutions for real DFT and test problems affecting designers today. Among the presenters was Mentor’s own Tessent DFT flows product manager, Vidya Neerkundar. Vidya talked about the technologies available to DFT and test engineers to enable the new chips being developed specifically for artificial intelligence applications.

The potential uses for artificial intelligence processing are vast, estimated at $65.6 billion by analyst group IBS, Inc., and is growing. The key to success in the highly competitive AI processor business is getting to market fast.

AI chips differ from traditional CPU and GPUs in a few key ways: the designs are very large, they use many replicated processor cores, and have memories distributed within the cores.

These new design characteristics can create new challenges for the entire design and test flow, particularly for time-to-market.

DFT and test engineers are quickly adopting new DFT software solutions and flows to get their designs done on time, including:

- DFT and ATPG solutions that can exploit AI chip regularity

- Inserting DFT logic at RTL, before logic synthesis

- Eliminating iterations between DFT and test during silicon bring up

The Tessent tools support all of these strategies for faster time-to-market for AI chips.

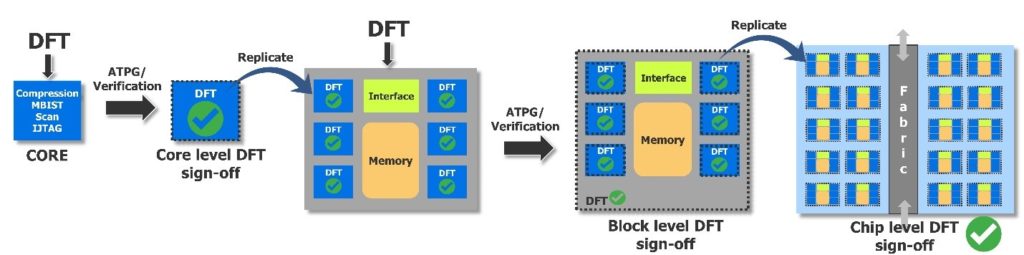

Hierarchical DFT accelerates time-critical tasks and keeps DFT out of the critical path. Hierarchical DFT lets you do all the work at the core or core-group level, then replicate any levels of hierarchy to the top-level. (Figure 1). Graphcore used hierarchical DFT to cut DFT time by 4X.

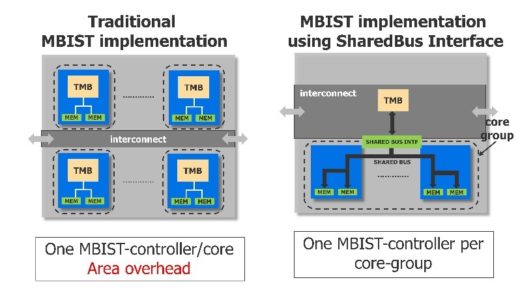

With hierarchical DFT, you can also implement MBIST using a shared bus interface (Figure 2). This single interface between the MBIST controller and all the memories in a core has many benefits, including:

- Reduction of routing at the parent level

- Reuse of functional memory access for test

- Core is DFT ready for replication

- Timing and layout/placement not impacted by DFT

Technologies that enable group-level hierarchical DFT include channel broadcasting, ability to control low power switching activity post silicon, and memory shared bus.

Inserting and verifying DFT logic at RTL also cuts DFT time and lends more flexibility to the DFT implementation. At the SVDFT conference, another speaker from Samsung presented their success using the Tessent RTL flow to meet a very tight, 2 month DFT schedule.

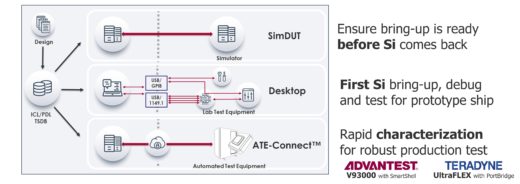

Finally, eliminating the iterations during test pattern bring up and debug saves a huge amount of time. The traditional test bring up requires several iterations between the DFT group (for test scheduling, test optimization, characterization, diagnosis, and debug) and the ATE. You can use a simulator to ensure bring-up is ready before silicon comes back. At first silicon bring up, there is a desktop bring-up environment that gives DFT engineers control of the process. Finally, the Tessent ATE-Connect technology bridges the gap between DFT and ATE. Graphcore completed test bring-up with Tessent in 3 days using the desktop solution, eliminating the use of ATE completely. Enflame achieved bring-up in 7 days.

Learn more about these solutions in the whitepaper, AI Chip DFT Techniques for Aggressive Time-to-Market.