DFT architectural tips: testing of asynchronous sets/resets

Most designs have some asynchronous sets or resets. Uncontrollable sets/resets can lower test coverage. This video discusses how to handle asynchronous sets/resets and how to test hierarchical blocks independently even if they have a common source.

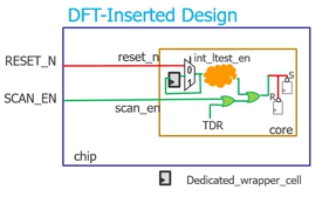

To manage asynchronous sets/resets, designers add control logic. But first, the sets/resets need to be defined at the RTL or gate-level and then evaluated through DRC checks to learn if the asynchronous sets/resets can be controlled. Sometimes, they need to be disabled during test. Tessent users can control the override of the sets/resets with test data registers via an IJTAG network.

The sets/resets need to be disabled during shift, and enabled during capture. In this video, Vidya Neerkundar describes the DFT logic that can be used to disable and enable sets/resets.

Within a chip, there may be hierarchical regions (or blocks, or cores) with asynchronous sets/resets. If they are at the boundary of a physical layout region, dedicated wrapper cells are inserted to control those sets/resets. Neerkundar describes how this core-level set/reset control aids in testing multiple cores at different times, independently of other blocks or parent levels.

If you are looking for tips on how to better handle asynchronous sets/resets to improve test coverage, we recommend watching Neerkundar’s short video.

Comments

Leave a Reply

You must be logged in to post a comment.

where is the video?

Thanks for alerting us to the missing video. When we changed from Mentor to Siemens, some links didn’t survive. I’ve embedded the video directly into the blog post.