Scan Insertion for better ATPG

By Vidya Neerkundar, Mentor Graphics

Good scan insertion can make a difference in the quality of your automatic test pattern generation (ATPG)…

When implementing hierarchical DFT for very large designs, it is more important than ever to get scan insertion right. A scan insertion tool should provide testability analysis, design rule check (DRC) debugging, test logic insertion, scan cell insertion, and scan chain stitching. It must also be able to handle very large designs and manage hierarchical DFT methodologies.

Testability analysis, which requires comprehensive DRC capabilities, is very important. Tessent Scan analyzes and helps improve design testability, so that once scan is inserted, the ATPG tool will be able to generate patterns that achieve high test coverage. DRCs check (for starters) that scannable registers can be controlled, clocks can capture data, scan chains can trace properly, data is stable and RAMs can be controlled.

Once a design exceeds 50 million logic gates, creating patterns on the full flat design late in the design flow becomes unnecessarily inefficient. With hierarchical DFT, the pattern generation is performed concurrently on the blocks early in the design phase, taking DFT out of the critical path. Tessent Scan now includes new features and improved usability for implementing hierarchical DFT. It supports both dedicated and shared wrapper cells. Shared wrapper cell analysis handles many corner cases, which results in fewer dedicated wrapper cells and lower area overhead. Multi-mode scan chains ensure that scan chains for both internal and external modes are created.

After flagging testability issues, Tessent Scan can automatically fix many of them. Some designs require gate level changes to address DRC issues. For example, something as simple as an uncontrollable reset signal could make the design untestable. Tessent Scan can automatically insert logic gates to address all DRC issues. The integrated Tessent DFTVisualizer lets you visually inspect and debug the scan chains and correct any remaining problems. Tessent DFTVisualizer shows the design in various views such as schematic, design structure, waveform, library, data, hierarchy, and additional views to facilitate viewing and troubleshooting.

For chain stitching, Tessent Scan ensures that the resulting chain shifts safely. It manages the merging of different clock domains and clock edges onto a chain with proper ordering or the insertion of additional lock-up cells. It also includes chain balancing, ordering from a scan DEF file, stitching pre-existing chains in sub-blocks and supporting wrappers for hierarchical DFT.

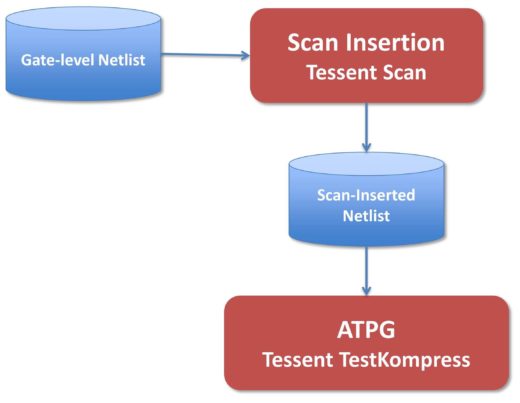

Tessent Scan is built on the same Tessent Shell platform used as the Tessent TestKompress® and Tessent FastScan™ ATPG tools. This means that you can leverage the same powerful scripting and automation environment The hand-off from scan insertion to ATPG is further simplified by Tessent Scan generating the required ATPG setup files.

Tessent Scan turns a gate-level netlist into a design that is completely ready for scan testing and pattern compression.

For an overview of Tessent Scan features, watch this short video