DDR4: Not Your Grandfather’s DDR

A long time ago, when DDR first came out, some of you may remember that it was difficult to design the interface. In my old board design team, we simulated the interface quite a bit to make sure that the system would function when the boards came back.

Then of course, the “been-there-done-that” attitude set in, and DDR became a design-by-numbers interface to push the schedule. Then came DDR2, which had many similarities to DDR. By the time DDR3 came out, many people didn’t even bother to simulate the setups at some of the slower speeds. They’re largely leveraged from a previous design, so why bother?

And then comes DDR4. This is the new guy in town who you can sense is a bit different. Questions come up:

- What, you don’t have a fixed Vref?

- You’re going to have a new threshold every time you power up? Then how do you know whether you’re the signal is a 1 or a 0 if I don’t know what the threshold is beforehand?

- What do you mean you’re going to flip all the bits?

Then maybe it starts to sink in:

Maybe I should simulate this. So, just how good are the IBIS models for this anyway? Can I trust them at these higher speeds?

These are many of the questions we answered, along with our partners at Fujitsu and Micron, in the paper that has was nominated at DesignCon for a best paper award: DDR4 Board Design and Signal Integrity Verification Challenges.

In the first half of the paper, we discuss the details of DDR4. What exactly are Pseudo-Open Drain (POD) and Data-Bit Inversion (DBI), and why the Vref is so dodgy? It will give you good background information about how DDR4 is different from DDR3.

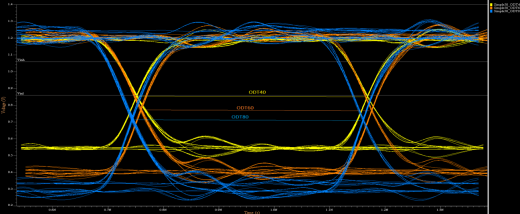

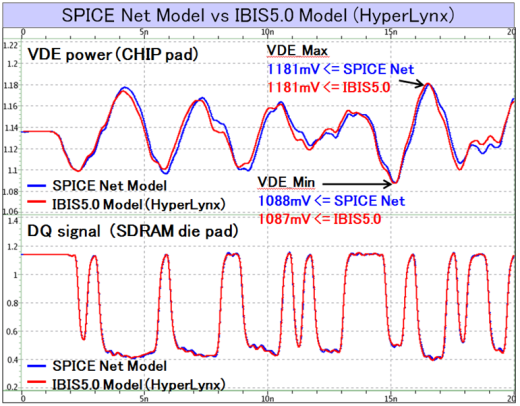

In the second half, we compare the simulation results of a large setup between the older IBIS 4.2 spec, the newer IBIS 5.0 spec, and a transistor level Spice model. Spoiler alert: the IBIS 5.0 results very closely match the transistor level Spice models – at a small fraction of the time needed to simulate.

If you are designing a DDR4, and would like to confirm your board, this paper is a helpful reference in deciding what needs to be analyzed before and after releasing the board.