Calibre IC Design in 2025: AI, 3D IC advancement and shift-left strategies drive verification excellence

Siemens Calibre IC Design continued to set the standard for digital, analog and 3D IC sign-off in 2025. We introduced or expanded breakthrough solutions, helping engineering teams stay ahead of the curve through smarter workflows, advanced analytics and platform flexibility.

Let’s take a look at some highlights of 2025.

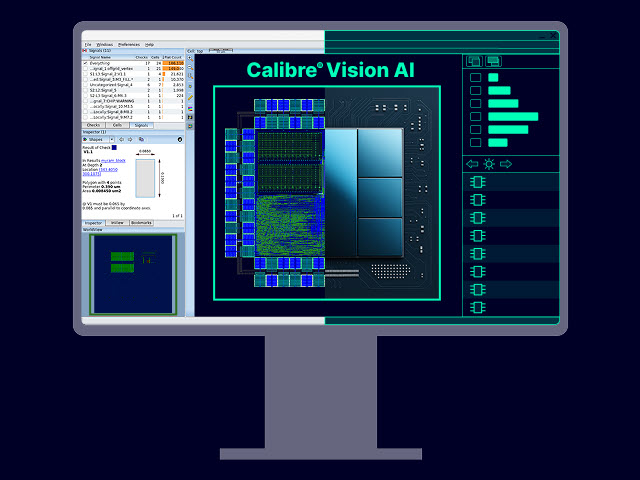

Accelerating debug and analysis with Calibre Vision AI

The role of artificial intelligence in chip verification is redefining how teams interact with DRC error data and debug environments. Siemens recently launched Calibre Vision AI, an innovative platform that applies machine learning to automate violation classification, prioritize issues, and deliver actionable insight in minutes—even across the largest SoCs.

At the 2025 TSMC OIP Forum, David Abercrombie shared the Calibre Vision AI story in a session titled “Leveraging AI to accelerate debug with Calibre Design Solutions.” They described how the innovated Calibre Vision AI tool streamlines error clustering, shortens root-cause analysis and enables interactive layout navigation for faster fixes.

The TSMC OIP event brings together one of the largest contingents of TSMC and Siemens customers and focuses on the EDA enablement to run designs at TSMC. This year AI enabled solutions were a focus in the TSMC and all EDA vendor presentations.

You can read about Calibre at TSMC OIP in this news release.

Want to hear more about Vision AI?…

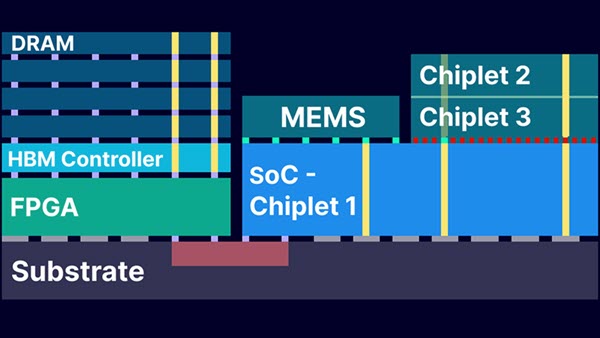

Expanding capabilities for 3D IC sign-off and reliability

3D IC and advanced packaging place new demands on verification tools, requiring specialized checks for power integrity, reliability and interconnect stress. The launch of Calibre 3DStress, the latest product in the Calibre 3D IC portfolio, marks a pivotal step, offering a purpose-built engine for simulating thermo-mechanical stress and reliability effects across stacked die assemblies. Engineers can now verify mechanical and thermal constraints in context, well before tapeout.

To learn how customers are using Calibre 3DStress, watch these presentations from the 2025 User2User conference:

- Innovative chip-package stress analysis for ICs using Calibre 3DStress

- Calibre 3DStress: advanced methodology for assessing IC reliability and performance

Meanwhile, growing customer adoption of Calibre 3DPERC continues to enable robust electrical rule checking in complex 3D designs. Calibre 3DPERC extends Calibre’s proven PERC methodology to cover vertical interconnects, through-silicon vias and multi-die integration, supporting next-generation SoCs and chiplets. Listen to Matthew Hogan, the PERC product manager, describe the value of Calibre PERC and 3DPERC.

In demanding markets where reliability and system integration are non-negotiable, these new offerings keep Calibre at the forefront of advanced packaging sign-off. Learn more in this technical paper, Calibre 3DPERC: Your key to robust ESD solutions for 3D ICs.

Accelerating sign-off with scalable shift-left methodologies and tools

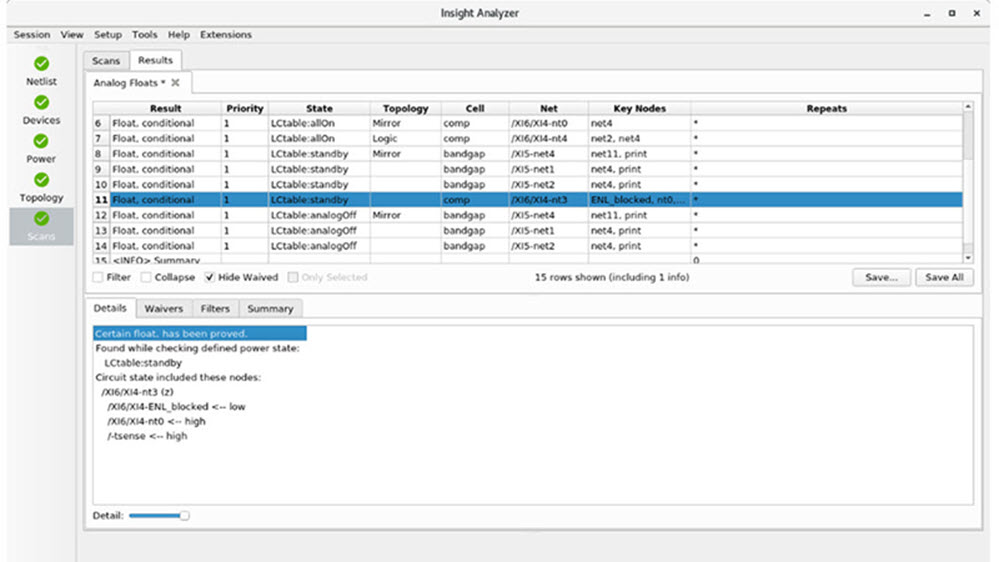

Design success increasingly depends on shifting verification and analysis left—catching errors earlier in the flow and enabling rapid iteration. Siemens Calibre continues to lead this transformation by delivering tools and methodologies that reduce the time to tapeout.

This year’s highlights include the growing adoption of Insight Analyzer, which is helping teams detect hard-t-find leakage issues across power domains before physical design. It pairs Calibre sign-off accuracy with powerful, interactive analysis. By visualizing violations in layout and context, teams can prioritize critical fixes and resolve bottlenecks faster than ever. Learn more about Insight Analyzer in this blog: Transforming pre-layout IC reliability analysis with Siemens Insight Analyzer.

Calibre supports AWS Graviton5

This year, we were excited to announce support for Calibre on Arm-based AWS Graviton processors, which deliver 20% performance improvements and more than 30% compute cost reductions on AWS Graviton4 compared with other AWS instances. As early adopters of AWS Graviton5, we saw an additional 30% performance boost, unlocking faster verification and time-to-market for our customers.

We were thrilled to support the breakthrough processor and watch it unlock new levels of efficiency, flexibility and cloud-optimized scalability for our customers. Read our announcement.

Calibre success, in our users’ own words

Finally, Siemens continues to support user learning and community engagement through the User2User conference. The U2U content library offers on-demand access to best-practice sessions and technical insights from industry leaders, fostering collaboration and continuous improvement.

Looking ahead: Smarter, faster, more reliable verification

The Calibre tool suite stands at the center of modern verification, enabling design teams to tackle the toughest challenges in AI-driven debug, 3D IC reliability and shift-left productivity. As chips grow more complex and customers demand higher yields, Siemens continues to deliver solutions that empower users—from hands-on verification engineers to CAD managers and executives.

If you’re ready to leverage the new Calibre innovations or want to see what 2026 has in store for sign-off, explore the Calibre Design Solutions product page and join the conversation at upcoming Siemens events.