From translator to powerhouse: Calibre V2LVS second generation redefines LVS verification

By Wael ElManhawy & Samar Abd El-Hady

Ever feel the squeeze of shrinking design nodes and the ever-growing complexity of System-on-Chip (SoC) designs? You’re not alone. In our fast-paced world of silicon, reducing verification runtimes and boosting signoff confidence are paramount. And right at the heart of this intricate dance, bridging your RTL design intent with transistor-level layout verification, sits Verilog-to-LVS translation.

Any hiccup in this critical step can lead to costly delays, frustrating rework, or even suboptimal silicon. That’s why we’re thrilled to share some exciting news about a major leap forward in this space: the second-generation Calibre Verilog-to-LVS (V2LVS).

What does V2LVS do?

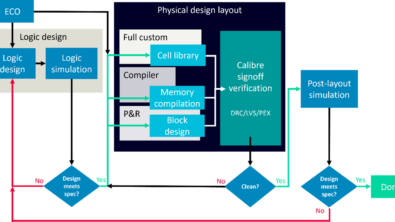

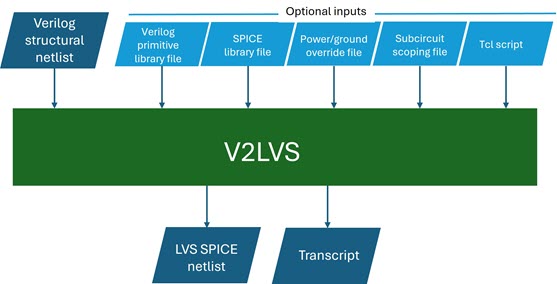

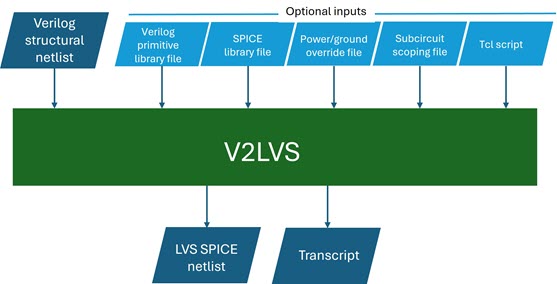

Calibre V2LVS is a vital component of the Calibre IC verification process. Think of it as a super-smart translator. It takes your structural Verilog netlists – which describe how your design is put together at a high level – and converts them into SPICE netlists. The SPICE netlists are then used by tools like Calibre nmLVS for accurate Layout Versus Schematic (LVS) checking and Calibre PERC for reliability verification. Essentially, it ensures that what you designed in your Verilog matches what you’ve laid out physically (figure 1). Pretty crucial, right?

The process usually starts with a structural Verilog netlist, which V2LVS checks for correct syntax. If you have multiple Verilog design files or even primitive library files, you’d typically concatenate them into single files before feeding them into V2LVS. This translation step is vital because it creates the detailed, transistor-level description that downstream verification tools need to do their job thoroughly.

Time for an upgrade: A leap forward in LVS verification

The original V2LVS tool was a workhorse, automating this translation for years. However, as design teams grew and project scopes expanded, its single-threaded, monolithic architecture started to show its age. Imagine trying to run a huge, complex factory with only one assembly line – it works, but it can get bogged down quickly! The previous approach limited its scalability and efficiency, especially with today’s massive netlists. We needed something more capable, more efficient, and more insightful to keep up with today’s demanding design cycles, avoid resource bottlenecks, and speed up job turnaround.

The second-generation V2LVS isn’t just an update; it’s a transformation! We’ve evolved V2LVS from a basic translation utility into a robust, multifunctional platform. Our goal? To give you faster, more intuitive debugging tools, enhance the usability and performance of your LVS verification flow, and shift left the performance – delivering earlier, more effective results in your verification lifecycle, saving time and headaches down the road. To learn about a “shift left” approach to LVS, read this blog post: Faster design verification with Calibre nmLVS Recon Compare.

Under the hood: architectural and performance boosts

The second-generation Calibre V2LVS is a major milestone, transforming a crucial utility into a sophisticated platform. The core change in this second generation is a completely new architecture. The first V2LVS was monolithic, focused solely on Verilog-to-SPICE translation. The new design is modular and flexible, letting different parts of V2LVS run independently and be optimized separately. This isn’t just about speed; this new setup also opens the door for future innovations, better design insights, and easier debugging automation. Plus, it sets the stage for even broader integration within the Calibre ecosystem.

Let’s talk about the impressive performance gains:

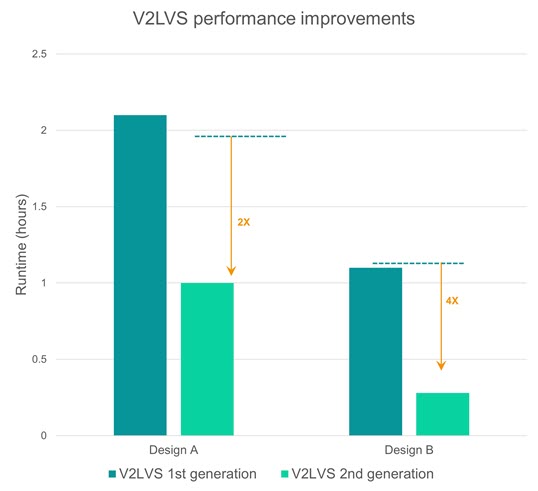

- Parallel module execution across threads: In previous versions, V2LVS operated on a single CPU/thread, executing all its modules one after another. This was a real bottleneck for large and complex netlists. The new architecture is much smarter: it allows different V2LVS modules to run on separate CPUs simultaneously. This innovation has shown significant speedups – we’re talking up to 4 times faster on real customer designs! It’s important to know that this isn’t yet full multi-threading (where the same module processes different parts of the design at the same time), but it’s a huge step forward, and full multi-threading is already being developed for even more speed. Figure 2 shows performance improvements of the new V2LVS.

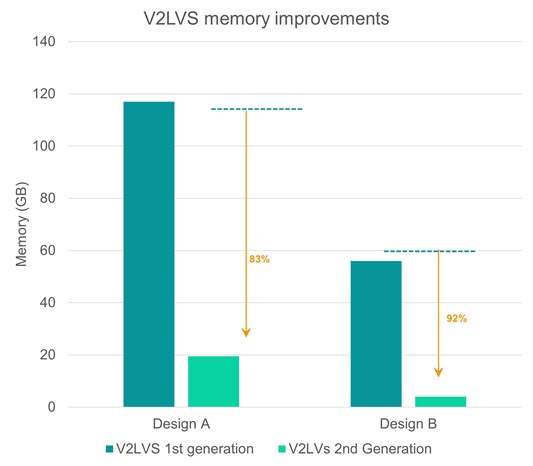

- Reduced memory footprint: Through smart architectural and algorithmic changes, V2LVS now uses much less memory – by as much as 92% in some tested scenarios! This is a massive advantage. Imagine being able to process designs that previously wouldn’t fit in memory, or running your verification flows much more efficiently in memory-constrained environments or on cloud platforms. This improvement directly translates to better scalability and lower operational costs. Figure 3 shows memory improvements for V2LVS.

Better debugging and user experience

Another big focus was making V2LVS easier to use, especially when it comes to debugging. Engineers often struggle with finding mismatches between master and duplicate subcircuits in the schematic netlists. The second-generation V2LVS aims to simplify this with a suite of new features:

Detailed V2LVS logs:

- Instance conversion progress: For truly massive tasks (think over 10 million instances), V2LVS now shows you real-time updates on conversion progress. No more staring at a frozen screen, wondering if it’s working or crashed!

- Module statistics: You get detailed statistics for each module, including its name, the number of contained ports, the number of nets, and the number of instance calls with total pin connections. This gives you a much clearer picture of what’s happening inside V2LVS and where resources are being used.

- Cumulative summaries: For every 10,000 modules converted, you’ll receive a cumulative summary. This provides regular checkpoints and insights into the overall progress, which is super helpful for long runs.

- Resource usage metrics: Memory and execution time are now reported for each stage of the process, along with the total program runtime. This is invaluable data for profiling your flows, identifying performance bottlenecks, and optimizing your setup for future runs.

Improved duplicate reporting: Two key enhancements here make debugging duplicates much less painful:

- You now have more control over how many duplicate warnings show up in the logs, so you can focus on the most critical ones without being overwhelmed.

- There’s a detailed duplicates report that includes the full paths to both master and duplicate instances, and it highlights exactly what’s different between them. This helps you quickly pinpoint the source of the mismatch.

Smarter Power/Ground Net Renaming: V2LVS creates a rename file for nets that have more than one text label. Before, it was possible for power/ground nets to get renamed by mistake. This might seem like a small detail, but it could cause big LVS and ERC problems downstream. The new version ensures that power and ground nets keep their original, intended names during the renaming process, maintaining their integrity for all subsequent verification steps.

What this means for you: Real-world benefits

Customers already using the second-generation V2LVS are seeing clear benefits that directly impact their projects:

- Faster turnaround times in LVS verification: This is huge for meeting tight deadlines and iterating quickly on designs.

- Significant memory savings on large SoC designs: This allows for more complex designs to be verified, or for existing designs to be verified more efficiently, potentially even on cloud platforms.

- Enhanced visibility into translation and mismatch diagnosis: No more guesswork! The detailed logs and reports mean engineers can understand exactly what’s happening and quickly resolve issues.

- Improved monitoring and debugging of large-scale designs: The new features provide the tools needed to manage and troubleshoot even the most complex verification flows.

These advantages aren’t just speeding up tape-out schedules; they’re also building more confidence in verification results. This helps teams work more effectively and deliver higher quality chips, which is what it’s all about!

Looking ahead

The second-generation Calibre V2LVS is a significant development, transforming a crucial utility into a more advanced tool. With multi-module parallelism, massive memory reductions, expanded reporting, and a clear roadmap toward full multi-threading, V2LVS is truly setting new benchmarks for Verilog-to-LVS translation.

As validation continues and new features roll out, Calibre V2LVS will remain a core technology, helping ensure accurate and timely circuit verification for today’s most complex semiconductor designs. It’s all about making your life as an engineer easier and your designs more robust.

Curious to see the impressive metrics, dive into the architectural specifics, and get the full technical rundown? We’ve just scratched the surface here! For all the intricate details, performance graphs, and a comprehensive look at how these enhancements were achieved, be sure to check out the full technical paper: The future of V2LVS: Faster, smarter second-generation Calibre V2LVS | Siemens Software

Frequently asked questions (FAQ)

Q1: What is Calibre V2LVS, and why is it crucial for semiconductor design verification?

A1: Calibre V2LVS (Verilog-to-LVS) is a vital part of the Calibre IC verification process. It acts as a “super-smart translator,” converting high-level structural Verilog netlists into detailed SPICE netlists. These SPICE netlists are then used by tools like Calibre nmLVS for accurate Layout Versus Schematic (LVS) checking and Calibre PERC for reliability verification. It’s crucial because it ensures that your initial design intent in Verilog precisely matches the physical layout of your chip, preventing costly errors and delays.

Q2: What are the key advancements and performance improvements in the second-generation Calibre V2LVS?

A2: The second-generation Calibre V2LVS represents a significant transformation. It has a completely new, modular architecture that allows different V2LVS modules to run in parallel across multiple CPUs, leading to up to 4 times faster performance on real customer designs. Additionally, it offers a massive reduction in memory footprint, using up to 92% less memory in some scenarios, which lets you run verfication on larger and more complex SoC designs.

Q3: How does the new Calibre V2LVS enhance the user experience and debugging process for engineers?

A3: The second-generation Calibre V2LVS significantly improves the user experience and debugging by offering more detailed and insightful logs. It shows real-time instance conversion progress, comprehensive module statistics, cumulative summaries and resource usage metrics (memory and execution time) for each stage. It also provides enhanced duplicate reporting with more control over warnings and detailed reports highlighting differences, plus smarter Power/Ground net renaming to prevent downstream LVS and ERC problems. These features collectively lead to better visibility and faster issue resolution.