An introduction to advanced verification techniques for IC design symmetry

By Jonathan Muirhead

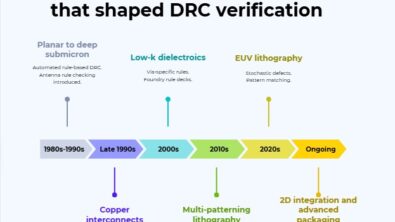

Integrated circuit (IC) design, particularly for analog and radio frequency (RF) circuits, involves meticulous attention to detail in order to ensure not only good manufacturability but also high performance silicon. Central to this process are the concepts of matching and symmetry, especially in topological structures like differential pairs and current mirrors. So, let’s briefly explore the evolution of these principles and recent advancements in checking techniques to ensure compliance.

Why symmetry matters

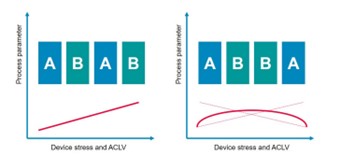

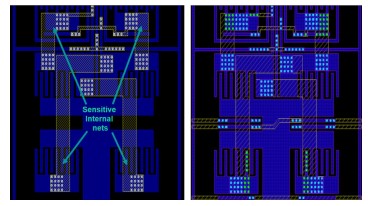

Symmetry isn’t just about aesthetics. In IC design, symmetry is crucial for the functionality and reliability of circuits. Identically-drawn MOSFETs in differential pairs must remain essentially identical throughout the layout lifecycle to maintain the same electrical performance. Figure 1 illustrates how symmetry can reduce the impact of stress and across-length variation (ACVL).

Traditional symmetry techniques

Techniques like common centroid design are employed to ensure that devices maintain symmetry around a central axis, which is critical for minimizing mismatches caused by process variations during chip manufacturing. This involves placing devices in such a way that they are symmetrically distributed around a central point or axis ensuring that any variations in manufacturing affect both devices equally, thereby maintaining their matched characteristics.

Challenges in maintaining symmetry

However, achieving and maintaining symmetry isn’t always straightforward. A differential pair MOSFET with schematic symmetry does not guarantee layout symmetry. Additionally layout context can influence overall symmetry. Cell or block routing, metal fill, and neighboring circuits or lack thereof can all impact the electrical characteristics and, therefore, symmetry matters. This has led to an extension or evolution of design requirements for symmetrical design.

Modern design requirements

Evolving design requirements

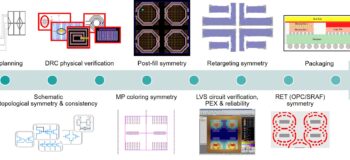

As technology advances, the complexity of designs and the requirements for process compatibility have increased. Symmetry now extends beyond simple geometric layout concerns to encompass the entire design cycle, from initial floorplanning to final packaging.

Correct-by-construction and parametrized cells

Modern electronic design automation (EDA) tools offer features like correct-by-construction (CRC) techniques and parametrized cells (pCells), which aid in maintaining symmetry. However, these tools often fall short when dealing with all the intricacies of modern designs. CRC techniques primarily focus on physical placement without considering circuit structure, reliability, robustness, and other advanced design for manufacturing (DFM) and yield considerations. While CRC processes might automatically place pCells correctly from a physical perspective, routing the associated pins, post-processing the pCells with fill, and considering the electrical aspects of the nets, voltage domains, and other aspects of symmetry matching still pose significant challenges for layout designers.

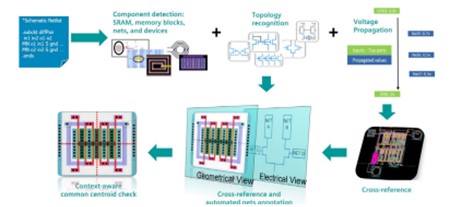

Symmetry at the netlist level

To address these challenges, advanced techniques are used to identify symmetry at the netlist level, making it electrically driven (figure 2). Although the front-end design does not directly impact the mask, its electrical and functional aspects are critical in driving the back-end design. This approach helps create electrically-aware/context-aware patterns composed of single multi-finger devices or groups of devices. Advanced electrically-driven symmetry verification can catch front-end symmetry issues early, preventing them from becoming time-consuming and difficult-to-correct downstream errors.

Advanced symmetry techniques

Floorplanning and DEF macros

During floorplanning, the symmetry of DEF macros is checked to catch early placement issues, and the main buses are checked for routing symmetry. Any small misalignment in the blocks not only impacts the matching requirements but also tends to generate an overwhelming number of design rule checking (DRC) violations and layout vs. schematic (LVS) discrepancies that will impede tapeout schedules. Post-layout simulations and expensive point-to-point (P2P) measurements are often required to address these issues, highlighting the importance of early symmetry checks during floorplanning.

Context-aware symmetry checks

Sensitive blocks and devices, which are hard to identify geometrically, are verified through topological patterns in the schematic/netlist. This “context-aware” approach helps ensure the consistency of complex devices, such as sense amplifiers in memory arrays. For instance, checks that combine both electrical and topological patterns can be used to verify the consistency of these amplifiers, ensuring that they operate correctly despite process variations.

Pre- and post-fill symmetry

Design filling is critical for meeting chemical-mechanical polishing (CMP) requirements. Modern fill processes can benefit from incorporating symmetry checks to ensure that both the original design and the filled layout maintain required symmetry and matching (figure 3). This step is key for meeting fabrication requirements while also achieving consistent device performance.

Benefits for established nodes

Even designs on established nodes can benefit from advanced symmetry verification. Applications like differential signal arrays and antennas, which require consistency and symmetry, can leverage these techniques to ensure robust and reliable designs. For instance, I/Q channel arrays, which handle differential signals, require precise matching to function correctly. Advanced symmetry verification helps achieve this by ensuring that the physical layout matches the intended electrical performance.

Upgrading traditional techniques

There are two successful methods for upgrading traditional techniques:

1. Pattern/property-aware analysis

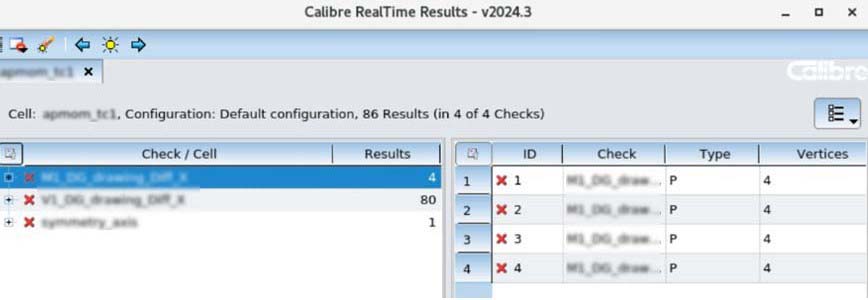

Traditional symmetry checking methods are often manual or computationally intensive, providing simple pass/fail results without aiding in debugging. Advanced techniques use pattern/property-aware analysis to verify various symmetry requirements and facilitate easier debugging. This approach not only addresses basic exact symmetry constraints but also includes the advanced requirements of fuzzy symmetry, which allows for minor tolerances in symmetry specifications. Figure 4 shows an example of the intuitive symmetry checking debugging interface, following a pattern-based symmetry analysis of a metal-oxide-metal capacitor.

2. Fuzzy symmetry

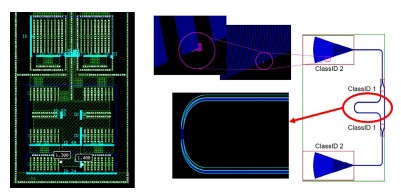

Fuzzy symmetry allows for tolerance by area or length, enabling designers to waive subtle differences that do not impact the design’s robustness. This capability is particularly useful in applications with strict tolerance requirements, such as MEMS and SiP. By allowing minor deviations from perfect symmetry, fuzzy symmetry helps designers focus on significant issues while ignoring inconsequential variations. Figure 5 shows an example opamp and silicon photonics curvilinear structures with minor symmetry differences that could be ignored to prioritize debugging of the major differences.

Out-of-the-box solutions

The Calibre nmPlatform integrates advanced symmetry checking functionalities, enabling interactive and batch process verification. Designers can access pre-coded checks and configure them without custom coding, streamlining the verification process. Calibre pattern matching symmetry capabilities, integrated with tools like Calibre PERC, provide easy-to-use, XML-controlled checks that can be invoked interactively or run as a batch process.

Interactive and batch process checking

Calibre’s pattern matching symmetry capabilities can be invoked interactively or run as a batch process, allowing for flexible and efficient symmetry verification. This approach ensures that designers can quickly identify and address symmetry issues, reducing the risk of time-consuming errors during the later stages of the design process.

Conclusion

As IC design becomes more complex, maintaining symmetry and matching for critical circuits is more important than ever. Advanced verification techniques and tools like Calibre nmPlatform help designers to efficiently find and fix symmetry issues, ensuring high performance and reliable designs. By leveraging these advanced techniques, designers can achieve robust, high-quality designs that meet the demands of modern technology, reducing the risk of errors and improving overall design cycle efficiency.

To learn more about Calibre’s pattern matching symmetry checking, read the full technical paper Advanced symmetry checking in IC layout design and verification.

Bonus! Recently added to our video library, here is access to a quick video introducing the latest developments in our Pattern Matching tools that are part of Calibre’s Shift left initiative, empowering designers to identify and resolve issues earlier in the design flow, ultimately reducing time to signoff. Watch it here: Calibre productivity and reliability enhancement solutions