Optimizing design implementation with Calibre LEF/DEF technology

By James Paris and Armen Asatryan

Ever hear the saying “When all you have is a hammer, everything looks like a nail”? Can you drive that screw into a block of wood with that hammer? Sure…sort of, but you’ll probably get better results and accomplish the task more easily with a screwdriver. Even if it’s a really good hammer.

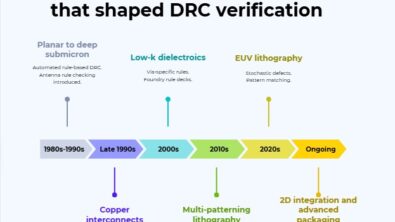

The same can be said when running integrated circuit (IC) design and verification tools. You can run your full-chip design rule checking (DRC) on early, incomplete data, and you’ll get some valid results mixed in with many results that only exist due to the current state of the design. Then you can spend a lot of time hammering out the difference between the two (see what I did there?). Alternatively, you can choose to use a solution that is best suited for the task and which enables you and your team to target valid critical issues in your current design flow stage.

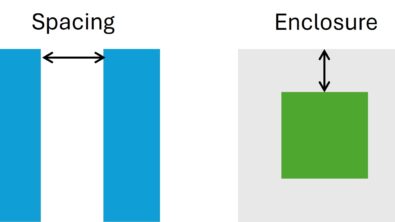

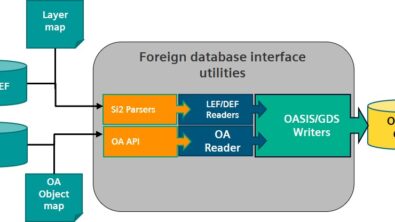

The Calibre LEF/DEF technology links place and route (P&R) design data to core Calibre physical verification and design enhancement flows. Focused selective rule decks that check for specific relevant issues at various design implementation stages help optimize your overall design flow by enabling more and faster iterations while focusing your team’s effort on actionable results that provide real value.

Ready to trade your hammer in for a more productive toolset? Explore the use of Calibre LEF/DEF technology solutions that map P&R design objects to Calibre physical verification flows, and incremental DEF output from Calibre that reads design enhancement objects back into the P&R design environment, in our technical paper, Data format conversions streamline parallel SoC design implementation & physical verification flows.