Custom layout designers…Want to know a secret? You can close DRC faster. A lot faster…

By Srinivas Velivala

Design rule checking (DRC) closure is a “tax” that custom layout designers must pay at all process nodes. Ask all layout designers what they would do if they had more time in their tapeout cycle, and the answers are likely to be a list of changes they would have made to optimize the layout design quality and get the most out of their power, performance, and area (PPA) goals. The complexity of DRC closure at advanced nodes (20nm and below) is well understood and supported by the electronic design automation (EDA) community. What is rarely acknowledged, however, is the time it takes to close DRC at mature nodes, and the impact this time has on the quality of the layout design. Every minute spent finding and fixing DRC errors takes valuable time away from design PPA analysis and optimization.

The Calibre RealTime Custom integration enables custom layout designers working at mature nodes to close DRC with significantly improved productivity by bringing interactive signoff-quality DRC into the design environment. No more waiting for hours to see the impact of your edits on DRC fixes—instead, designers get DRC feedback in seconds. Enabling the Calibre RealTime Custom functionality in design environments is a breeze, and the simple intuitive GUI enables designers to start using the integration with little to no ramp-up time. Accelerating DRC productivity earlier in the design flow has never been easier!

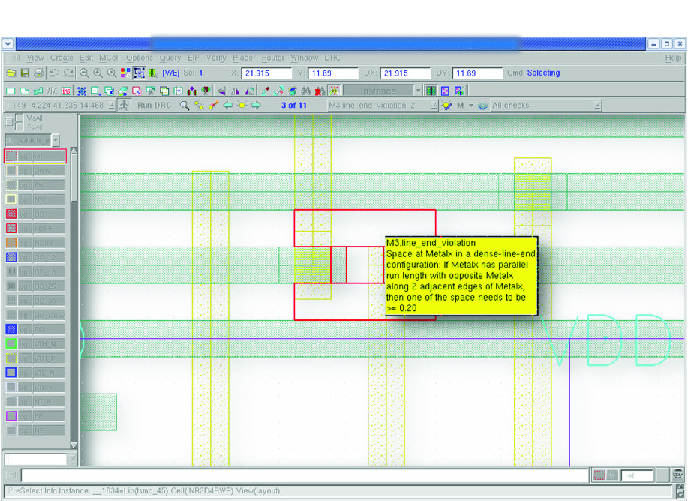

Microchip has a robust Calibre nmDRC flow that is optimized for batch signoff DRC runs, but they wanted to improve their DRC productivity earlier in the design flow. Adding Calibre RealTime Custom in-design signoff-quality DRC checking enabled their design teams to find and fix DRC issues by running DRC on a local design window using only the relevant checks for that design stage. The Calibre RealTime Custom tool also allowed layout designers to quickly and easily create check recipes to focus on high-value checks. With immediate DRC feedback available in seconds, Microchip designers saw a 60X improvement in DRC runtime vs. full batch runs on local windows, which translated to a 2-4X increase in their overall DRC productivity. They were also able to use the interactive DRC feedback from the Calibre RealTime Custom tool (and the extra time they now had!) to perform what-if analyses to make optimum DRC fixes.

The physical verification (PV) engineers at Microchip used the Calibre RealTime Custom tool during final tapeout review to find critical DRC errors that were directly gating the tapeout. They loaded the design into the Calibre DESIGNrev environment, and used Calibre RealTime Custom interactive DRC feedback to perform a what-if DRC analysis and make the optimum fix. They were able to perform multiple quick iterations with the Calibre RealTime Custom tool, enabling them to report back to block owners which fixes going forward would eliminate final DRC issues to get to tapeout faster.

If you’d like to see the details of Microchip’s experience with the Calibre RealTime Custom tool, and learn how you can accelerate DRC productivity from early design to final tapeout, please download a copy of our paper, Microchip sees significant productivity gains in mature node custom IC design with in-design signoff DRC.

By the way, the Calibre Realtime Custom tool isn’t really a secret…tell all your friends!