Automate via insertion for improved design reliability and performance

By Fady Fouad, Esraa Swillam, and Jeff Wilson – Mentor, A Siemens Business

IR drop and EM issues slowing down your tapeout? Automated push-button via insertion provides DRC/LVS-clean vias that significantly improve IR drop and EM results. We discuss…

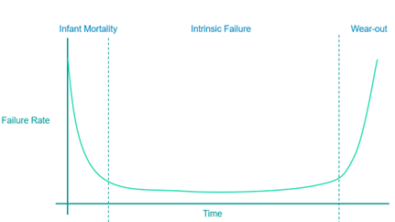

As every electrical engineer is well aware, power structure design has become more challenging with each advance in technology nodes. In particular, voltage drop (IR) and electromigration (EM) issues have grown significantly in both number and impact. Integrated circuit (IC) designers have to find new ways to manage the increasing resistance from narrower metals, which has a direct effect on reliability and yield.

With the power grid width being pre-determined, the most effective means of lowering resistance is to insert additional vias into the layout. However, the custom scripts traditionally used to add vias are simply too complex and time-consuming to create and run in advanced node designs, given the need to control different stacks, complex spacing rules, different enclosures, and via count per width. Design teams invariably end up extending their time to market, impacting competitive positioning and profitability.

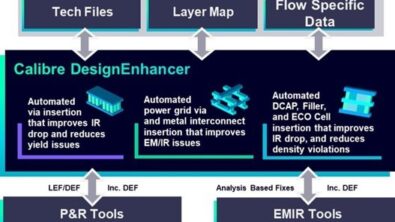

Enter the Calibre™ YieldEnhancer PowerVia utility, which provides a “push-button” via set-up and insertion process, delivering an easy, automated flow that inserts additional correct-by-construction vias as needed to reduce IR drop and EM issues, and improve design performance and reliability.

The PowerVia utility flow relies on manufacturing requirements supplied by the foundry to determine correct-by-construction requirements for via insertion. This flexibility enables the PowerVia utility to work with any foundry for any process, while ensuring the inserted vias are compliant with all design rule checking (DRC) and layout vs. schematic (LVS) requirements.

Think it sounds too good to be true? To determine how use of the PowerVia utility would affect both their design quality and tapeout schedules, Mentor, a Siemens business worked with IC design companies to implement and evaluate the PowerVia solution in production designs. Results showed significant improvements in EM/IR results, including substantial reductions in current density violations, appreciably improving design performance and reliability with minimal impact to design schedules.

Want to get the details? Download a copy of our white paper, Reducing IR and EM issues with automated via insertion, and be on your way to better-performing, more reliable designs.