SoC IO ring checking: going beyond ESD verification

By Abdellah Bakhali – Mentor, A Siemens Business

Better SoC IO ring verification means more accurate and consistent product reliability. New automated checks help designers identify and correct errors early in the design flow. Learn more here…

Aristotle once suggested the whole is greater than the sum of its parts, meaning that a collection or aggregate of individual pieces can generate a unity or a synergy that transcends the simple sum of the items. That’s true for any living organism (hopefully, you are more than just an assemblage of bones and tissues!), and it’s true for SoC IO rings, too.

When SoC designers combine multiple IPs into a SoC layout, they must also create a SoC IO ring that not only provides the necessary reliability protection across the entire SoC, but also integrates all of the disparate IO ring rules for the IPs. All those IO rings must be compliant with their own unique set of design rules, but must also co-exist and operate in harmony with the whole.

Because of this amalgamation, though, SOC designers face some unique IO ring verification challenges. Traditionally, SoC IO ring verification is done manually, late in the design flow. That approach creates two major issues: not only is manual verification time-consuming and prone to human error, but any errors found are typically difficult to fix without creating additional errors, leading to a cascading delay in tapeout. That’s a synergy SoC designers would just as soon avoid!

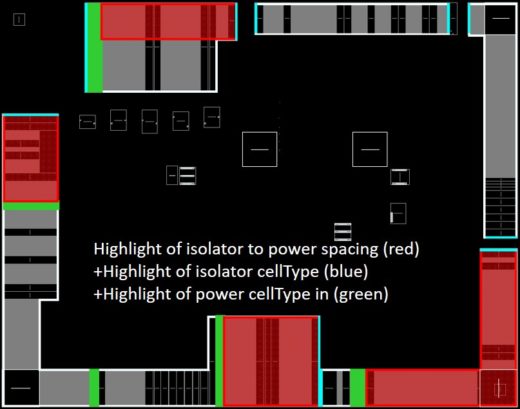

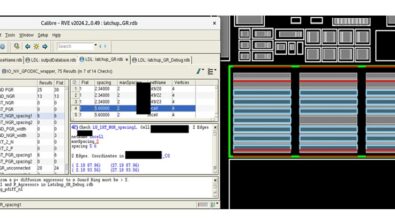

Fortunately, new options for automated IO ring verification are now practical and available. The Calibre PERC reliability platform uses an IO ring checker framework to provide a robust environment that verifies both IP and SoC IO placement rules with sign-off quality. The IO ring checker offer a unique capability to check any type of placement rules, not only covering electrostatic discharge (ESD) protection, but going beyond ESD verification to enable multiple reliability verification activities.

Even better, it can run on the first LEF/DEF floorplan out of P&R, meaning any errors can be corrected with minimal impact on the layout and the schedule. In most cases, SoC design teams can reduce days of reviewing down to hours.

If that’s the kind of synergy you’re looking for, download a copy of our white paper, Enhancing IO ring checks for consistent, customizable verification, and start your transformation. Because as Aristotle also said, ““For the things we have to learn before we can do them, we learn by doing them.”