HDAP connectivity verification—what’s your solution?

By Tarek Ramadan – Mentor, A Siemens Business

New HDAP designs like FO-WLP require package-level connectivity verification tools and processes. Learn how the Calibre 3DSTACK tool provides a significant advantage over traditional SoC LVS flows.

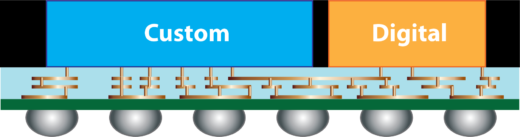

While high density advanced packaging (HDAP) is a fast-growing market, comprehensive package verification still has a ways to go. Unique package connectivity issues, such as missing or misplaced interposer/package bumps/pads, pin naming and text labeling issues, and the like, require new and enhanced verification techniques that can move across the entire package to ensure proper connectivity and performance. In the integrated circuit (IC) world, automated layout vs. schematic (LVS) verification ensures that the physical layout of the circuitry matches the design intent expressed in the SPICE netlist. Automated LVS hasn’t historically been popular in the packaging world because the number of components and required I/Os is usually small, so an “eyeball check” of a simple spreadsheet or bonding diagram has usually sufficed. However, as HDAP evolves and its use expands, the need for an automated LVS-like flow to detect and highlight more complex package connectivity errors has become apparent.

I n its simplest form, an automated package LVS-like flow should ensure that the interposer/package GDSII correctly connects die to die (for multi-die systems) and die to C4/BGA bumps (for both single die and multi-die systems) as intended by the designer. Electronic design automation (EDA) tool suppliers are responding to this growing need with new verification solutions that address the specific needs of the HDAP market. With its native support for packaging file formats, automated analysis of HDAP connectivity verification requirements, and integrated assembly-level DRC and LVS checking, the Calibre® 3DSTACK™ tool from Mentor, a Siemens Business, provides a significant advantage over traditional SoC LVS flows.

n its simplest form, an automated package LVS-like flow should ensure that the interposer/package GDSII correctly connects die to die (for multi-die systems) and die to C4/BGA bumps (for both single die and multi-die systems) as intended by the designer. Electronic design automation (EDA) tool suppliers are responding to this growing need with new verification solutions that address the specific needs of the HDAP market. With its native support for packaging file formats, automated analysis of HDAP connectivity verification requirements, and integrated assembly-level DRC and LVS checking, the Calibre® 3DSTACK™ tool from Mentor, a Siemens Business, provides a significant advantage over traditional SoC LVS flows.

For example, an HDAP with a high number of I/Os typically has many die VDD/VSS to package VDD/VSS connections. Using the traditional LVS approach, multiple VDDs/VSSs in the same “.SUBCKT” are reduced to one VDD/VSS, which makes it impossible to verify all power/ground connections. That’s okay for system-on-chip (SoC) verification, because a broken VDD/VSS connection that is not detected will be caught in future electrical analysis. However, because the electrical analysis flows are not 100% established for HDAP signoff, designers can’t neglect those power/ground issues by assuming they will be detected downstream. The Calibre 3DSTACK verification solution includes the following features in its power/ground connectivity checking:

- Highlighting “floating” bumps/pads geometrically

- Checking the location for interposer/package pins

- Checking GDSII-only opens/shorts

- Highlighting bumps that don’t have complete physical connectivity

Even with an automated package LVS flow in place, however, it can be challenging to debug package connectivity errors efficiently, particularly if the number of errors returned is huge. Package designers can simplify and speed up the debugging process if they are aware of some basic issues that can result in numerous errors, such as using different pin naming conventions in the system source netlist and the interposer package layout.

To see the full explanation of these issues, and learn how designers can use a solution like the Calibre 3DSTACK tool with automated package LVS capabilities to resolve them, download our white paper, Package designers need assembly-level LVS for HDAP verification. Streamlining and accelerating the package verification flow, while ensuring comprehensive connectivity coverage and accurate results, supports and encourages the growth of existing and emerging package technologies, and the new and innovative products they can deliver.