Shocking news about ESD protection!

By Derong Yan – Mentor, A Siemens Business

Electrostatic discharge (ESD) protection is critical for today’s electronic products, which require reliability in demanding environments and conditions. The Calibre PERC reliability platform provides efficient, accurate, automated checking of ESD requirements, even in complex SoC designs with billions of transistors.

Electrostatic discharge (ESD) can damage or destroy gate oxide, metallization, and junctions in an integrated circuit (IC). While ESD protection has always been a part of IC design and verification, it has become increasingly critical at advanced nodes, due to shrinking transistor dimensions and oxide layer thicknesses. At the same time, the growing die sizes of system-on-chips (SoCs), the increasing number of transistors being packed into them, means design teams are spending way more time and resources to run ESD checks.

The primary cause to date has been the way ESD checks are written and implemented. Traditional ESD checking requires design companies to write their own rule decks and implement checks using their standard design rule checking (DRC), layout vs. schematic (LVS) and electrical rule checking (ERC) tools. That doesn’t work very well, for a couple of reasons:

- With every design company writing their own ESD protection rules, there’s no consistency across the industry. That makes it hard for foundries to be sure that the right ESD protection is in place everywhere it should be.

- Standard DRC, LVS, and ERC tools are each designed to do one thing really well—and that one thing is NOT checking circuitry that requires a knowledge of both physical AND electrical design characteristics.

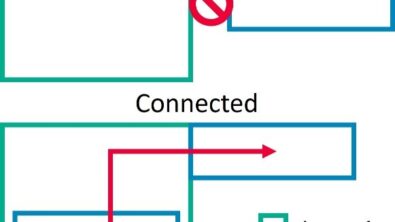

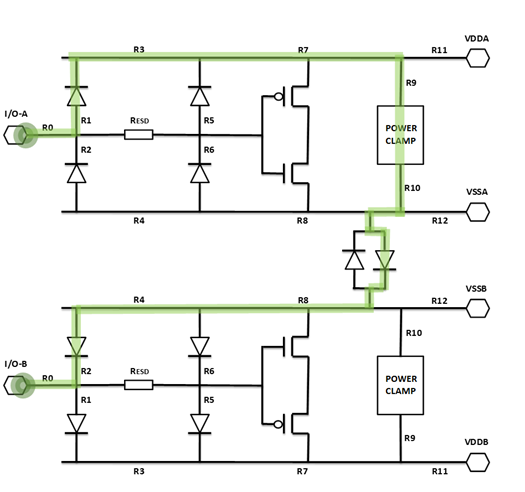

The Calibre PERC reliability platform solves both of those challenges in one tool. It uses an innovative logic-driven layout analysis that can combine physical and electrical design information to provide advanced verification for ESD, as well as other reliability conditions like electrical overstress (EOS), signals crossing multiple power domains, and advanced ERC. It’s integrated with the Calibre nmLVS™ tool to enable a layout extraction that can be used to identify topology information in the input layout design, eliminating the need for any manual intervention or manually-generated layout markers. Because it can go beyond traditional DRC, LVS and ERC, the Calibre PERC reliability platform can provide sign-off quality reliability checks at the intellectual property (IP), block, and full-chip levels.

But what about those custom rule decks, you say? Many leading semiconductor foundries now provide Calibre PERC rule decks, eliminating the need for customized rule decks and providing a standardized, repeatable, and efficient process you can implement to verify the most challenging reliability issues from first schematic, through SoC assembly, to the final layout. Calibre PERC rule decks included in process design kits (PDKs) typically check for the existence and connectivity of ESD devices, latch-up requirements, maximum current densities and maximum point-to-point resistance values along ESD discharge paths, and more. Not to worry, though—you can still create customized Calibre PERC checks to address any special design and verification needs.

But what about those custom rule decks, you say? Many leading semiconductor foundries now provide Calibre PERC rule decks, eliminating the need for customized rule decks and providing a standardized, repeatable, and efficient process you can implement to verify the most challenging reliability issues from first schematic, through SoC assembly, to the final layout. Calibre PERC rule decks included in process design kits (PDKs) typically check for the existence and connectivity of ESD devices, latch-up requirements, maximum current densities and maximum point-to-point resistance values along ESD discharge paths, and more. Not to worry, though—you can still create customized Calibre PERC checks to address any special design and verification needs.

Want to learn more, or see exactly how the Calibre PERC reliability platform can handle tricky design issues like maximum current density and point to point resistance checks? Our new white paper, Ensuring Robust ESD Protection in IC Designs, explains the requirements behind ESD protection schemes, and demonstrates how to use the Calibre PERC reliability platform to verify that they are properly implemented in your design.

What’s really shocking? Just how easy it is to step up your ESD protection process and improve your design reliability.