Solido Design Environment: A Solution for Variation-Aware and High Sigma Verification Challenges

In electronic design, staying ahead of the curve and utilizing cutting-edge tools for success is crucial. We’re excited to announce the launch of our comprehensive training course for the Solido™ Design Environment. This AI-powered design environment is used for SPICE-level design and verification, offering a unified nominal and variation analysis solution trusted by thousands of designers in high-performance computing, AI, IoT, automotive, and mobile applications to create competitive products.

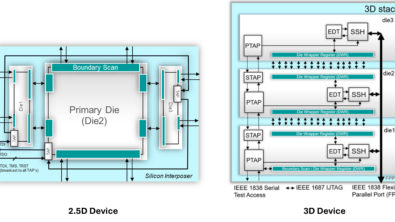

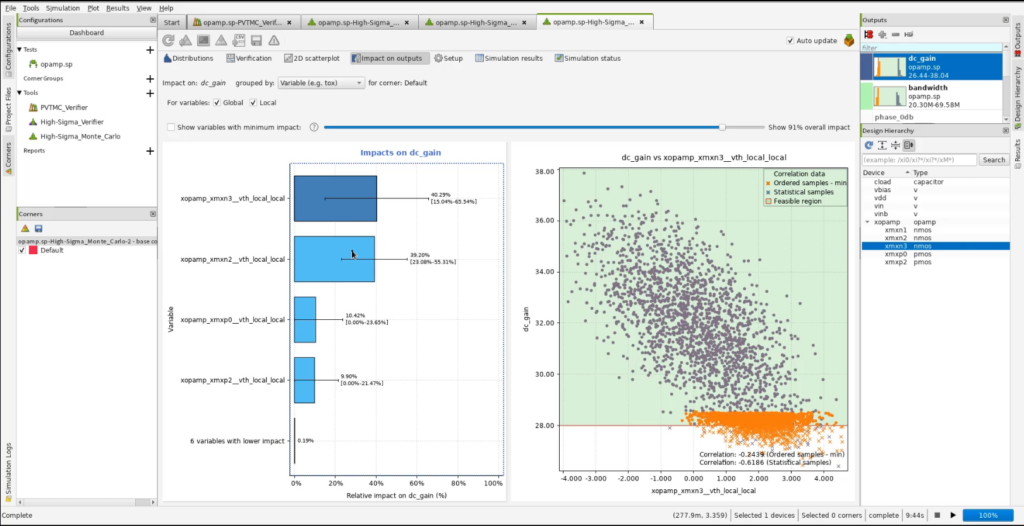

Using the Solido™ Design Environment, engineering teams can set up SPICE-level simulations for circuit measurements and regressions, analyze waveforms and statistical results, and handle nominal and variation-aware analysis, all in a single cockpit. Solido™ Design Environment can be used throughout the design process, from initial device sizing to advanced 6+ sigma variation analysis. The solution seamlessly integrates AI technology to perform production-accurate statistical yield analysis, at a fraction of runtime, compared to brute-force methods, and assist the user in identifying optimization paths, to improve circuit power, performance, and area. Adaptive AI powers orders of magnitude speed up for 3 to 6+ sigma at all corners with verified brute-force accuracy. Additive learning uses retained AI models to provide an additional 10x to 100x speed up. It also has assistive circuit optimization and analysis.

Our course will guide you through the various features and licensing schemes of the Solido™ Design Environment, ensuring you have a thorough understanding of its capabilities. You will become familiar with both the Graphical User Interface (GUI) and Command-Line Interface (CLI), allowing you to navigate and operate the software seamlessly.

You will learn how to set up and run simulations using Solido™ Design Environment, covering various flow models.

You will explore the integration between Solido™ Design Environment and Siemens Custom IC design tool, S-Edit.

You will discover how to back-annotate and cross-probe results seamlessly, enhancing your design workflow.

You will master the creation and interpretation of custom outputs and scripted outputs.

You will learn to generate compound measurements and analyze plots to gain valuable insights into your designs.

You will explore Solido™ Design Environment’s data and cluster management capabilities, ensuring efficient utilization of resources and maximizing productivity.

You will dive into key technologies within Solido™ Design Environment, including PVTMC Verifier, High-Sigma Monte Carlo, High Sigma Verifier, Hierarchical Monte Carlo, Fast PVT, DesignSense, and Cell Optimizer. You will explore their applications in yield analysis, variation analysis, and design optimization.

You will learn how to generate comprehensive reports and analyze results in various flows effectively. This feature will enable you to communicate your findings and insights clearly and concisely.

Hands-on lab exercises will complement the lectures, providing you with practical experience under the guidance of industry-expert instructors. These exercises will reinforce key topics and concepts discussed throughout the course.

Enroll today and unlock the full potential of Solido™ Design Environment. Gain the skills to perform statistical yield analysis, optimize circuits, and tackle complex variation analysis.

Let’s elevate your design capabilities to new heights!

To learn more and secure your spot on the course, visit our Siemens Xcelerator Academy website.

Get ready to master Solido™ Design Environment and excel in your analog and mixed-signal designs!

After completing the course, you can test your knowledge and differentiate yourself by taking our Certification Exam and earning a verified Solido Design Environment Level 1 digital badge!

Authors: Yarah Keelany, Shree Shourya NR, and Indu Yadav: Customer Training Engineers at Siemens EDA Learning Services