Enhance Test Time and Quality with Tessent Hybrid TestKompress/LogicBIST

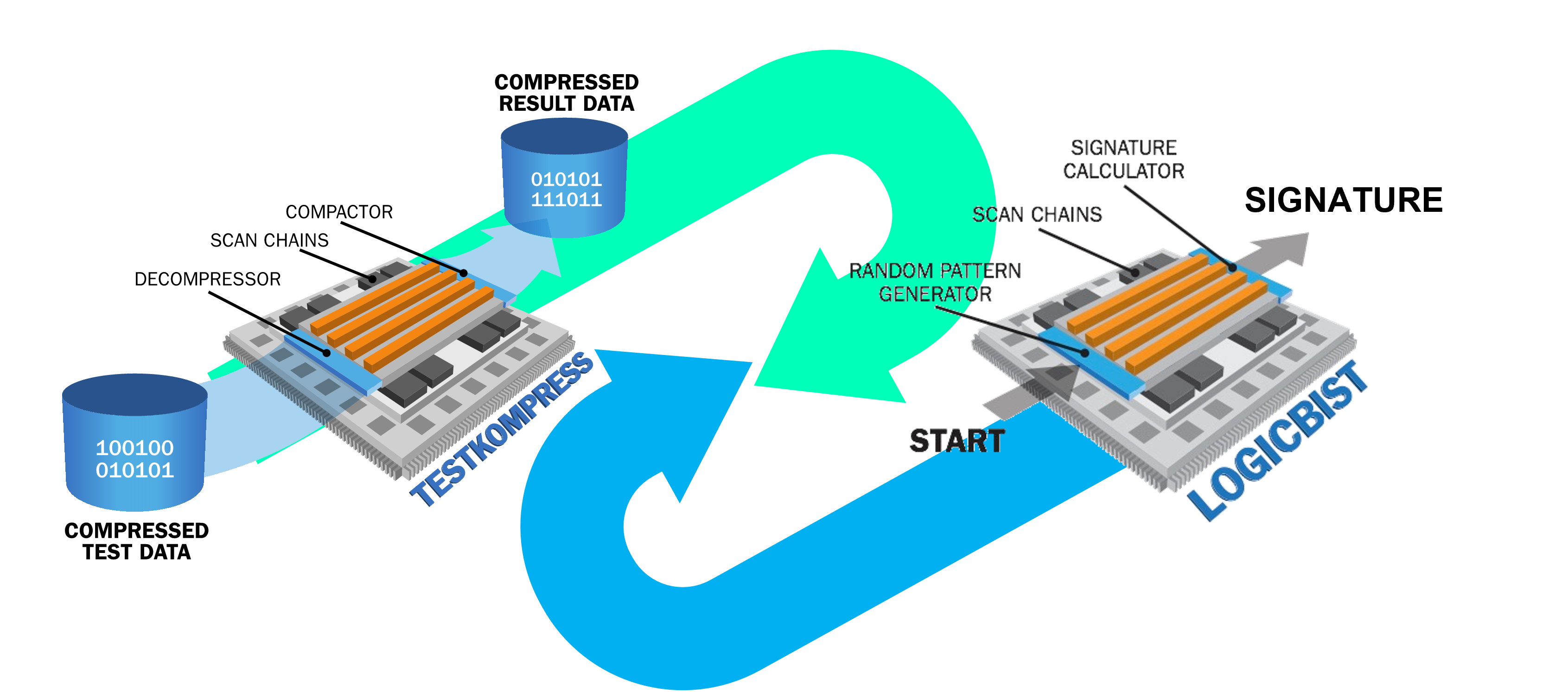

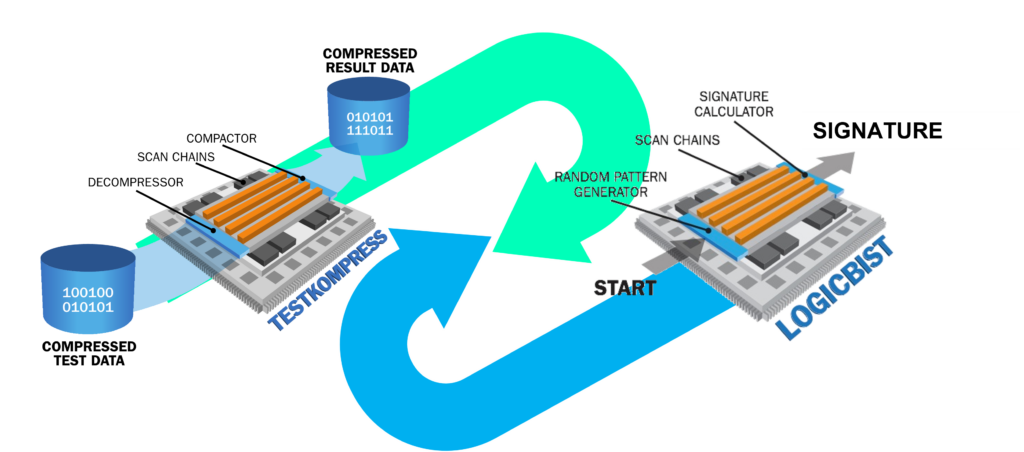

As a TessentTM software user, you’re probably familiar with TessentTM TestKompress software and TessentTM LogicBIST software (logic built-in self-test) for logic BIST insertion. Siemens combined both benefits in one “Hybrid TestKompress/LogicBIST” solution where compression IP is being re-used to apply BIST tests, reducing the hardware overhead compared to a separate implementation of TestKompress EDT (Embedded Deterministic Test) and logic BIST IP. This is done by re-using parts of the IP for EDT and logic BIST modes. This hybrid logic controls input test stimuli generation and output response comparison and is implemented separately for each EDT block.

The Hybrid TK/LBIST solution is the ideal, high-quality silicon test for safety-critical devices such as ICs in automotive and medical applications. The tool is integrated with the TessentTM software tool set, so combining this with other test IPs, like MemoryBIST and BoundaryScan, is easy.

The solution takes advantage of many similarities between the two approaches to deliver a highly efficient combined solution. It also combines the on-chip controller logic for both ATPG compression and logic BIST into a single block smaller in area than the two separate implementations. This comes with a reduction in the test time by combining LBIST’s quick detection of a large number of faults with the high-bandwidth application of random patterns followed by a much smaller set of compressed ATPG patterns to cover the remaining undetected faults, as well as test data volume reduction. It makes it possible to have in-system testing for that particular design. You’ll have the highest test quality compared to using TessentTM TestKompress or TessentTM LogicBIST alone.

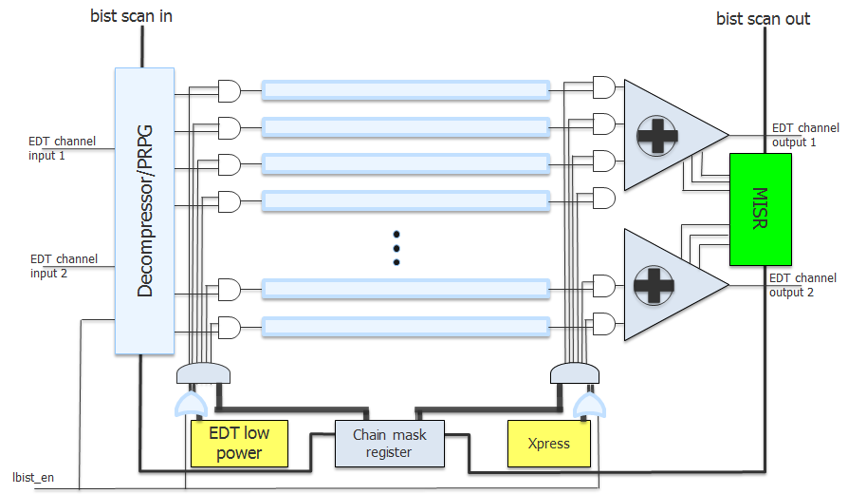

The figure illustrates the joint logic architecture of the Tessent Hybrid TK/LBIST solution. The embedded deterministic test and LBIST share most of the decompressor/PRPG and the compactor/MISR logic. In addition to area savings through having shared logic, you also save area because the hybrid approach requires fewer test points to be added to the design compared to standard LBIST alone.

The logic shown in light blue is shared between the two test modes. That includes the scan chains, combination decompressor pattern generator, chain mask register, and compactor logic.

The additional logic in yellow blocks is also used for compressed EDT mode. That includes the optional EDT low-power controller and the Xpress compactor control.

For logic BIST mode, the compactor output drives into the multiple input signature register, or MISR, to generate the signature.

The TessentTM Streaming Scan Network (SSN) is supported in the independent Hybrid TK/LBIST insertion flow. SSN effectively distributes scan data for the ATPG patterns by hosting EDT controllers with ScanHost nodes.

If you’d like to learn more about Tessent Hybrid TestKompress/LogicBIST, you can take our on-demand training course Tessent Hybrid TestKompress/LogicBIST by visiting the Siemens Xcelerator Academy page: Hardware & software applications courses | Siemens Software where you can have access to training videos, self-assessments, and lab exercises. Also, you can now earn a digital badge/level 1 certificate by taking our Tessent Hybrid TestKompress/LogicBIST Exam. If you successfully pass the Level 1 Certification Exam, you can display your digital badge on LinkedIn or your email signature.

For additional questions or assistance, contact a Siemens representative at xceleratoracademy_eda.disw@siemens.com.

Author: Nada Wahba, Senior Customer Training Engineer, Siemens EDA