Interchange format standard in hierarchical CDC and RDC analysis

For large designs with numerous asynchronous clocks and resets, there is a growing need to do clock domain crossing (CDC) and reset domain crossing (RDC) analysis in a hierarchical way. This allows parallelization of sub-block and noiseless analysis and helps reduce SoC runtime and speed closure of CDC and RDC issues at the SoC level. Conversely, it poses challenges for design houses using third-party IP in ensuring the compatibility of their hierarchical data models (HDM) in the case of multiple EDA tools usage.

Challenges and solutions in doing CDC and RDC analysis on a large design

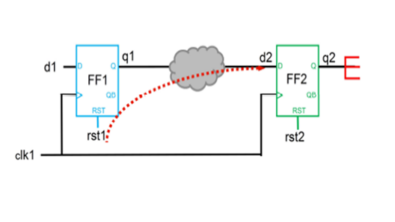

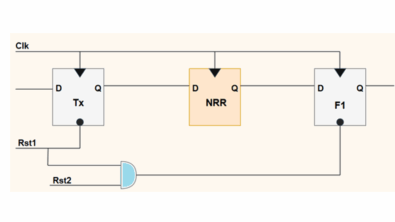

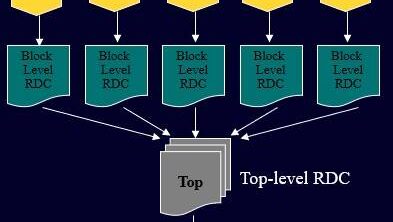

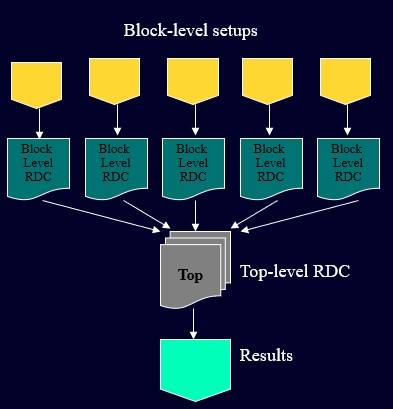

In today’s complex digital designs, the number of asynchronous clocks and asynchronous resets has become very large. The asynchronous nature of the clocks and resets cause metastability issues in designs. Designers need to implement correct CDC and RDC synchronization schemes on each of these asynchronous paths. To meet this challenge, designers tend to break up large designs into smaller sub-blocks. They do CDC and RDC analysis at the sub-block level. This helps to reduce the debug time and closure of any CDC or RDC issues in the design. Then they create HDM for each sub-block and use the HDMs at the top level to do final signoff of CDC and RDC analysis. This helps design teams achieve closure of any CDC and RDC issues faster and, hence, speed up the overall design cycle.

Figure 1. Bottom up generic CDC/RDC hierarchical flow.

Another industry trend in large projects is the use of IP from third-party vendors. To protect their IP, vendors rarely provide the register transfer language (RTL) source code. They prefer to provide HDM for their IPs. Currently HDM needs to be generated with the same EDA tool that customers will use to consume the HDM for CDC and RDC analysis at the SoC level. To resolve this problem a CDC Working Group was created within the Accellera organization. Currently, leading semiconductor companies are driving this effort and all large EDA companies who provide solutions to do CDC and RDC analysis support this effort. The goal of this Working Group is to create a standard format for HDMs so the models can be consumed by any EDA tool irrespective of the source of the generated model. This will help the design community tremendously by making them independent of any particular EDA tool to do their CDC and RDC analysis.

Anyone who is involved with and familiar with CDC and RDC analysis technology and would like to contribute to this initiative can join the Accellera CDC Working Group. Click on this link and follow the instructions to join the group as a participating member.