From Novice to Expert: Your Tutorial Roadmap at DVCon Europe 2025

In support of Verification Academy’s educational mission, Siemens is either directly sponsoring or contributing to the following five tutorials at the upcoming DVCon Europe 2025 on Tuesday October 14.

These presentations address a wide range of D&V topics, from novice to expert level: whether it’s the latest on applying Agentic AI technology to accelerate verification closure, HW-SW co-verification, to updates on important industry standards for low power D&V and Clock Domain Crossing (CDC) and Reset Domain Crossing (RDC).

And of course, please follow-up with our presenters and other domain experts at expo booth 21.

9:45am – 11:15am | Forum 7

1D: Data-Driven Approach to Coverage Closure ASIC Designs

Tulio Pereira Bitencourt, Rasadhi Attale, Samuel Man-Shun Wong, Po-Shao Cheng, and Anton Tschank

During the last few decades, the semiconductor industry has experienced an ever-growing complexity in integrated circuit (IC) designs. The requirements for chips have risen and with more tasks now being allocated into devices that must be area efficient, low power and operate at high frequencies, it becomes challenging to ensure that those marvels of technology work flawlessly before they go into production.

As the industry moves towards Intellectual Property (IP)-based approaches, where independent parts of chips are purchased and embedded to compose more robust and application-specific integrated circuit (ASIC) designs, Verification Engineers must now cope with increased complexity of highly configurable ICs while ensuring acceptable time-to-market. Moreover, relying on robust and straightforward Electronic Design Automation (EDA) tools and effective data-driven methodologies ensure that coverage targets can be met even in the most complex scenarios.

This tutorial aims to propose a novel data-driven approach to accelerate coverage closure on highly configurable ASIC designs. During the tutorial, the following topics will be covered:

Challenges of working with highly configurable IPs: Discusses the different aspects of verifying fully parameterized ASIC designs that leverage randomized parameters in thoroughly compatible testbenches and coverage metrics.

Requirement management and verification planning: Showcases the need for well-defined, mappable and machine-readable specifications, the creation of parameter-based verification plans, and the importance of end-to-end traceability for data-driven verification.

Early bug detection: Focuses on the importance of continuously monitoring metrics to identify gaps or issues early in the process. Introduces live simulations and alternatives to track historical regression data for optimized debugging.

Traffic light system & Unreachability: Presents the application of a traffic light system (i.e., green, amber and red waivers) for assessing coverage reachability under highly configurable environments.

Structure for effective regressions: Introduces a powerful and well-defined regression system capable of randomizing parameters, generating data (e.g., coverage, failures, etc.) and collecting failure signatures.

Accumulated coverage structure: Proposes a robust and straightforward procedure to generate and accumulate coverage metrics across all supported and randomized configurations.

Real-time and interactive dashboards: Highlights the value of real-time and interactive dashboards for acquiring an overall view of design/verification health and regression performance. Its advantages become clear when there is a need for scalable and efficient identification of issues in large permutations of IP configurations.

Powerful tools to enhance time-to-market: Wraps up the presented methodology and describes how to effectively use a mix of graphic, analytic and artificial intelligence/machine learning (AI/ML) options to accelerate Coverage Closure.

Therefore, the herein presented data-driven approach aims at effectively accelerating the coverage closure process of highly configurable ASIC designs by leveraging the presented state-of-the-art methodology and robust EDA options. The tutorial is structured to showcase a new methodology to cope with very complex real-world scenarios when dealing with highly configurable designs, as well as to present thorough details on how one can reproduce it.

11:30 AM – 1:15 PM, Forum 4

2A: CDC-RDC Standardization: Concepts & Status

Jean-Christophe Brignone

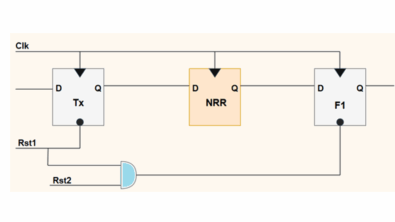

CDC-RDC analysis has evolved as an inevitable stage in RTL quality signoff in the last two decades. Over this period, the designs have grown exponentially to SOCs having 2 trillion+ transistors and chiplets having 7+ SOCs. Today CDC verification has become a multifaceted effort across the chips designed for clients, servers, mobile, automotives, memory, AI/ML, FPGA, etc., with focus on cleaning up thousands of clocks and constraints, integrating the SVAs for constraints in validation environment to check for correctness, looking for power domain and DFT logic induced crossings, finally signing off with netlist CDC to unearth any glitches and corrupted synchronizers during synthesis.

As the design sizes increased in every generation, the EDA tools could not handle running flatly and the only way of handling design complexity was through hierarchical CDC-RDC analysis consuming abstracts. Also, hierarchical analysis helps to enable the analysis in parallel with teams across the globe. Even with all these significant progress in capabilities of EDA tools, the major bottleneck in CDC-RDC analysis of complex SOCs and Chiplets is consuming abstracts generated by different vendor tools. Different vendor tool abstracts are seen because of multiple IP vendors; even in-house teams might deliver abstracts generated with different vendor tools.

The Accellera CDC Working Group aims to define a standard CDC-RDC IP-XACT / TCL model to be portable and reusable regardless of the involved verification tool.

As moving from monolithic designs to IP/SOC with IPs sourced from small/select providers to sourcing IPs globally (to create differentiated products), the quality must be maintained as driving faster time-to-market. In areas where the standards (SystemVerilog, OVM/UVM, LP/UPF) are present, the integration is able to meet the above (quality, speed). However, in areas where standards (in this case, CDC-RDC) are not available, most options trade-off either quality, or time-to-market, or both 🙁 Creating a standard for interoperable collateral addresses this gap.

This tutorial aims to remind the definitions of CDC-RDC Basic Concepts and constraints, as well as the description of the reference verification flow, and addressing the goals, scope, structure & deliverables of the Accellera CDC Working Group in order to elaborate a specification of the standard abstract model.

A status related to the last LRM version open to public review by Q2 will be presented.

11:30 AM – 1:15 PM, Forum 6

2C: Creating a Co-Simulation Environment for Questa Simulator Using QEMU

Telat Işık, Faruk Karaahmet, and Melike Karabalkan

This presentation will deliver step-by-step details on creating a co-simulation environment using QEMU for the Questa Advanced Simulator.

3:00 PM – 4:30 PM | Forum 4

3A: Unleashing the Potential of Agentic AI Within Design & Functional Verification

Darron May

In the rapidly evolving landscape of semiconductor design, the complexity and scale of digital circuits continue to grow exponentially. Traditional methods of Register-Transfer Level (RTL) functional verification are increasingly challenged by these advancements, necessitating innovative approaches to ensure robust and efficient verification processes. This technical workshop aims to explore the integration of Artificial Intelligence (AI) and Machine Learning (ML) into RTL functional verification workflows, showcasing new products and methodologies that leverage these cutting-edge technologies.

The workshop will feature a comprehensive overview of the current state of RTL functional verification, highlighting the limitations and bottlenecks faced by verification engineers. We will introduce a suite of new AI/ML-powered tools designed to enhance verification efficiency, accuracy, and coverage. These tools employ analytical, predictive, and generative AI to automate pattern recognition, detect anomalies, generate “right by construction” artifacts like code and assertions, significantly reducing the time and effort required for verification tasks.

Via the following presentations on “smart” automation for design and testbench creation, debug and regression acceleration, engine optimizations, and collaborative coverage analysis, participants will be able to map their needs to these new AI/ML-accelerated flows using faster engines, enabling faster engineers and optimizing resources with fewer workloads:

- Introduction to AI/ML in RTL Verification: Understanding the basics of AI/ML and their applicability to RTL verification.

- New AI/ML-Driven Verification Tools: Demonstrations of the latest products incorporating AI/ML engines, including their features, benefits, and use cases.

- Case Studies and Real-World Applications: Insights from industry leaders on successful implementations of AI/ML in RTL verification, showcasing tangible improvements in verification outcomes.

- Future Trends and Challenges: Exploring the future potential of AI/ML in verification and addressing the challenges associated with their adoption.

By the end of the workshop, attendees will have a deeper understanding of how AI/ML can transform their overall approach to RTL functional verification, driving innovation and efficiency in their verification processes.

Join us to stay ahead of the curve and harness the power of AI/ML to tackle the complexities of modern RTL D&V!

5:15 PM – 6:45PM, Forum 4

4A: Tutorial on the Improvement introduced by IEEE 1801-2024 (UPF4.0) Standard for the Specifications, Implementation and Verification of Low Power intent

Joshua Ong, Nathalie Meloux, Gabriel Chidolue, and Shaun Durnan

As advanced low-power architectures have become more pervasive in industry, the complexity of these architectures has driven new methodologies for the verification, implementation, and reuse of power intent specifications. Modern low-power designs place requirements that span from enabling more flexible IP design reuse to providing well-defined interfaces between analog and digital components in simulation. The IEEE 1801-2024 (UPF 4.0) standard provides several key enhancements that are required to keep pace with these innovations in low-power design.

This tutorial is based on the DVCon US 2025 workshop titled “Introduction of IEEE 1801-2024 (UPF4.0) Improvements for the Specification, Implementation and Verification of Low-Power Intent“; and will provide an overview of the enhancements to the standard from both conceptual and command levels.

New concepts such as virtual supply nets, refinable macros, and UPF libraries will be introduced, as well as re-architected features with respect to interfacing between analog and digital simulation and advanced state retention modeling for enhanced semantics.

While the new IEEE 1801-2024 standard provides numerous detailed clarifications and enhancements to the previous version, this workshop will focus on the key changes that will impact most designers and changes that enable new functionality.

Reference link: the complete DVCon Europe 2025 program grid.

Join us!

The Siemens EDA D&V Team