Accelerate Closure of Reset Path and Reset Domain Crossing Issues in Digital Designs

In today’s large, complex designs, multiple asynchronous resets have become the norm. The increase in reset domains is driven by complex SoCs using different controllers to manage more complex power management schemes and software-based resets.

In tight project windows, engineers tend to use waiver mechanisms and/or use constraints (i.e., setting false paths) to completely eliminate paths from reset domain crossing (RDC) analysis, which can result in RDC bug escapes. In a recent DVCon conference presentation, a design engineer declared “jihad” against such use of waivers and constraints to remove certain reset paths from being properly analyzed. Instead more reset domains and asynchronous resets in modern chips, along with faster designs, requires a proper RDC sign-off methodology to avoid chip-killing metastability, glitches, and other functional problems.

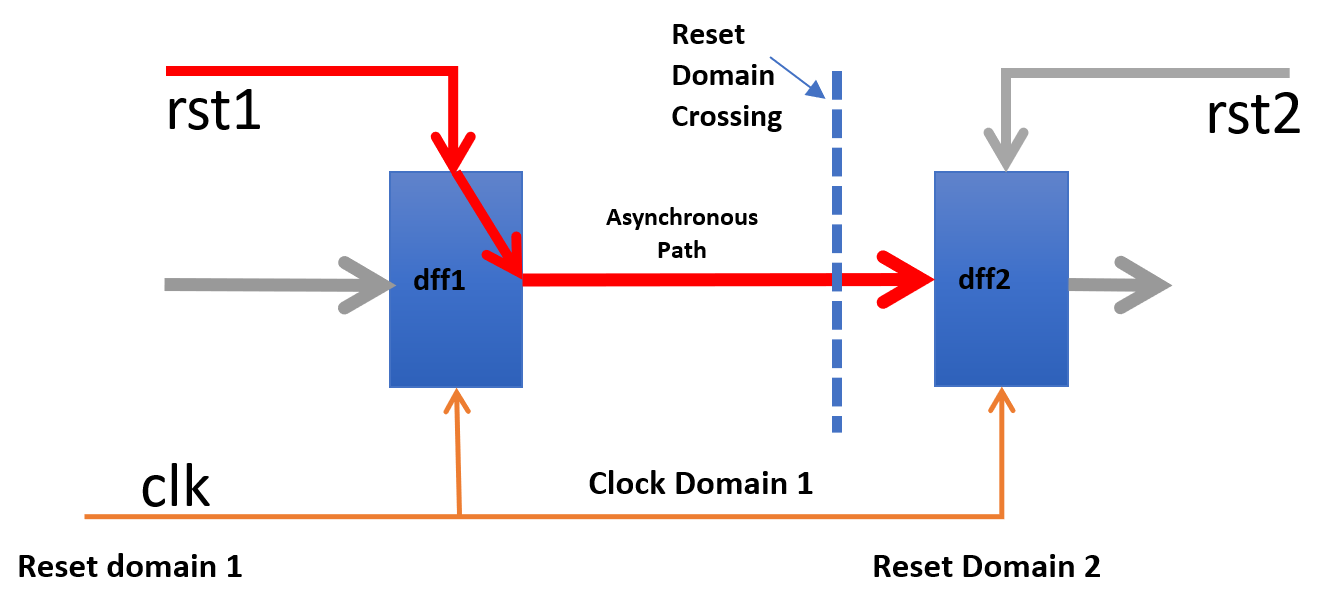

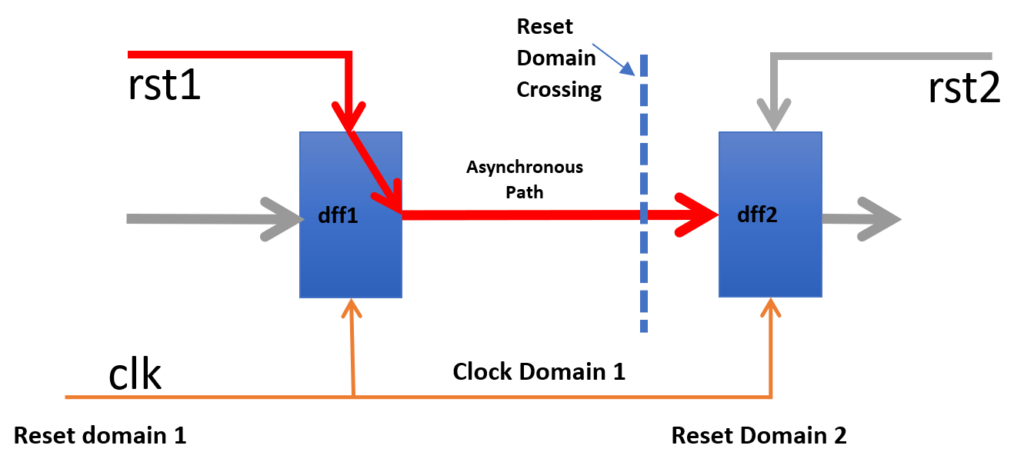

A RDC occurs when a path’s transmitting register has an asynchronous reset, and the receiving register has an uncorrelated reset or no reset. Metastability and loss of functional correlation are design errors that can occur from improperly implemented RDCs and asynchronous resets.

Figure 1. Reset domain crossing path.

Design engineers demand that any RDC tool should automatically recognize functional false paths and report them. This enables engineers to analyze all valid RDC paths that need to be looked at. This helps engineers to speed up RDC analysis closure with full confidence, while allowing a more directed focus on the identified, real issues that should be addressed in the design.

Instead of using wildcards to constrain certain mode selection signals in the design to filter out paths from RDC analysis, engineers should use tool specification flows to target the exact signals. Engineers can apply stable or constant values to clock paths during the functional mode. This helps to reduce any RDC bug escapes while maintaining the highest quality of RDC analysis.

To reduce power, sometimes engineers need to add non-resettable registers (NRR) on asynchronous reset paths to the registers. But this may result in RDC issues in the design. RDC analysis tools need to identify such asynchronous reset paths so that engineers can verify the validity of their presence in the design. To correctly address this issue, engineers need to define a new asynchronous reset domain on the last NRR.

RDC metastability analysis and debug is global, unlike CDC metastability analysis, which is local. The RDC analysis path can go from a source in one reset domain through an intermediate set of registers and modules to the destination register in a different reset domain.

RDC sign-off is becoming part of the sign-off flow before tape out, due to complicated power management schemes, security management schemes, I/O connections, configurations, and faster designs. It is vital to deploy a methodology that eliminates RDC bug escapes due to metastability, glitches, and functional correlation losses – while still delivering the optimal performance, power, and area for your designs within tight project windows.

To learn more about how analysis tools can save your team time and money while improving the quality of RDC results in your designs, please read the new white paper from Siemens EDA, Analysis of RDC Issues for Identifying Reset Tree Design Bugs for Noise Reduction.

Farhad Ahmed

Siemens EDA Questa R&D