Smarter DFT: an integrated flow for hierarchical designs (plus the best little DFT conference!)

The Silicon Valley DFT Conference is happening now! It’s chock full of industry experts presenting practical solutions (and it’s free!). The SV DFT conference is the sister conference to the successful SWDFT conference held in Austin, Texas. The focus of presentations is practical solutions to real problems in DFT and test. It’s being held Wednesday and Thursday – September 26-27th.

Wednesday is dedicated to a tutorial, “Interconnected IEEE Standards.” The instructors, one from Synopsys and one from Mentor, address the most popular test access standards and the most important aspects of each. These include IEEE standards 1149.1 (package/board connection and beyond), 1687 (instrument access through 1149.1), 1500 (core wrapping), and P1838 (3DIC test access). These standards can interact with each other and may rely on other IEEE standards to support automated construction, and design and use methodologies which will be addressed by the presenters.

The main conference day, Thursday, September 27th offers a morning keynote and 10 presentations from leading semiconductor companies, university researchers, a patent lawyer, and a couple of EDA technology/tool experts. One of the technology spotlight presentations is from the Tessent group at Mentor. Expert Vidya Neerkundar will give a quick overview of integrated Tessent DFT flows, with a focus on DFT for hierarchical designs.

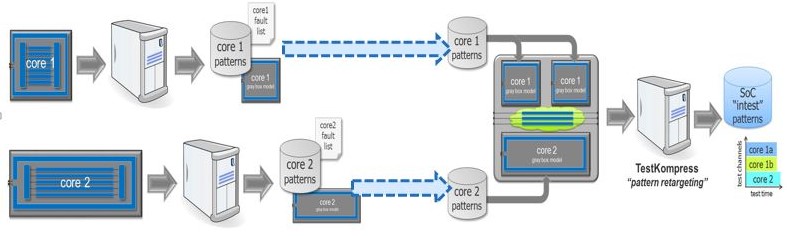

Hierarchical design is an increasingly common strategy as designs grow larger. According to the Wilson Research Group and Mentor Graphics, about 31% of designs have over 80 M gates, and 20% have over 500 M gates. A divide-and-conquer approach to DFT involves generating test patterns at the core level, then retargeting and merging them later.

There are compelling reasons to adopt a hierarchical DFT flow for your hierarchical designs; it reduces the number of chip pins needed for test, reduces ATPG runtime and memory footprint, and takes DFT work out of the critical tape-out path.

Neerkundar will cover the requirements for implementing hierarchical DFT, which includes building an integrated DFT flow through automation. Neerkundar will talk about the components of an integrated flow like the one Tessent offers. The Tessent tools are on a single platform (Tessent Shell) with powerful scripting capabilities, employ a plug-and-play IEEE 1687 infrastructure, simplifies data management, and automates your DRC (design rule checking).

You can learn more about Mentor’s Tessent flow in this free whitepaper Smart DFT infrastructure and automation are key to managing design scaling