Article Roundup: Timing Library LVF Validation For Production Design Flows, ABCs of PCBs – D for DRC, Embedding Software Algorithms in New Chip Applications Calls for New Verification Solutions, Aging Analysis Standard Solidifies Through Collaborative Effort, Oren Manor: Mentor Leading Way for Industry 4.0

- Timing Library LVF Validation For Production Design Flows

- ABCs of PCBs – D for DRC

- Embedding Software Algorithms in New Chip Applications Calls for New Verification Solutions

- Aging Analysis Standard Solidifies Through Collaborative Effort

- Oren Manor: Mentor Leading Way for Industry 4.0

Timing Library LVF Validation For Production Design Flows

SemiEngineering

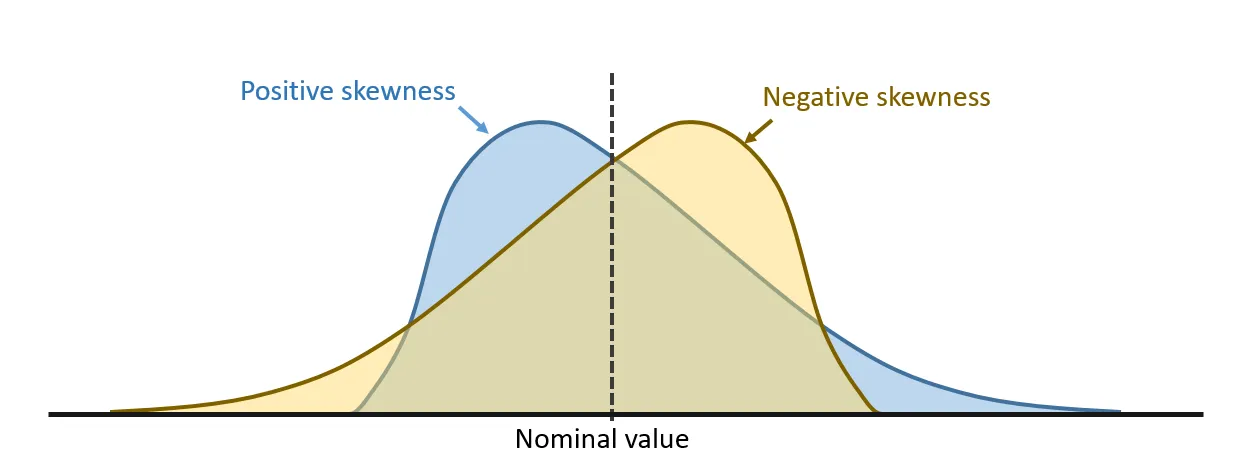

This article talks about why verifying Library variation format (LVF) is a crucial step for on-schedule silicon success and how Mentor’s Solido Analytics uses machine learning for broad-coverage LVF data, to help identify outliers and potential issues in the entire data set. Variation modelling using LVF allows chip designers to encapsulate statistical variation data to supplement nominal timing values, and is required for advanced process nodes 22nm and below.

This article talks about why verifying Library variation format (LVF) is a crucial step for on-schedule silicon success and how Mentor’s Solido Analytics uses machine learning for broad-coverage LVF data, to help identify outliers and potential issues in the entire data set. Variation modelling using LVF allows chip designers to encapsulate statistical variation data to supplement nominal timing values, and is required for advanced process nodes 22nm and below.

ABCs of PCBs – D for DRC

MentorBlogs

In this blog, the author takes a deeper look at how DRCs can aid in the design process. The designer may see tools with built-in DRCs that can be parameterized by the user and the option to create their own rules based on design requirements. The goal of these rules is to identify electrical, physical, or logical violations that may affect the integrity of the design. The blog further highlights some rules like component polarity, net name checks and more.

In this blog, the author takes a deeper look at how DRCs can aid in the design process. The designer may see tools with built-in DRCs that can be parameterized by the user and the option to create their own rules based on design requirements. The goal of these rules is to identify electrical, physical, or logical violations that may affect the integrity of the design. The blog further highlights some rules like component polarity, net name checks and more.

Embedding Software Algorithms in New Chip Applications Calls for New Verification Solutions

EEWeb

One of the desirable traits needed for improved verification is – a new design and verification flow that starts by modeling the SoC design at a high level of abstraction that includes the software algorithm typically written via Python. In this article, the author talks about how migrating such algorithms to cutting-edge SoC projects that power up AI, deep or machine learning, high-performance compute, automotive, 5G, and open-source ISA applications is a challenge.

Aging Analysis Standard Solidifies Through Collaborative Effort

SemiEngineering

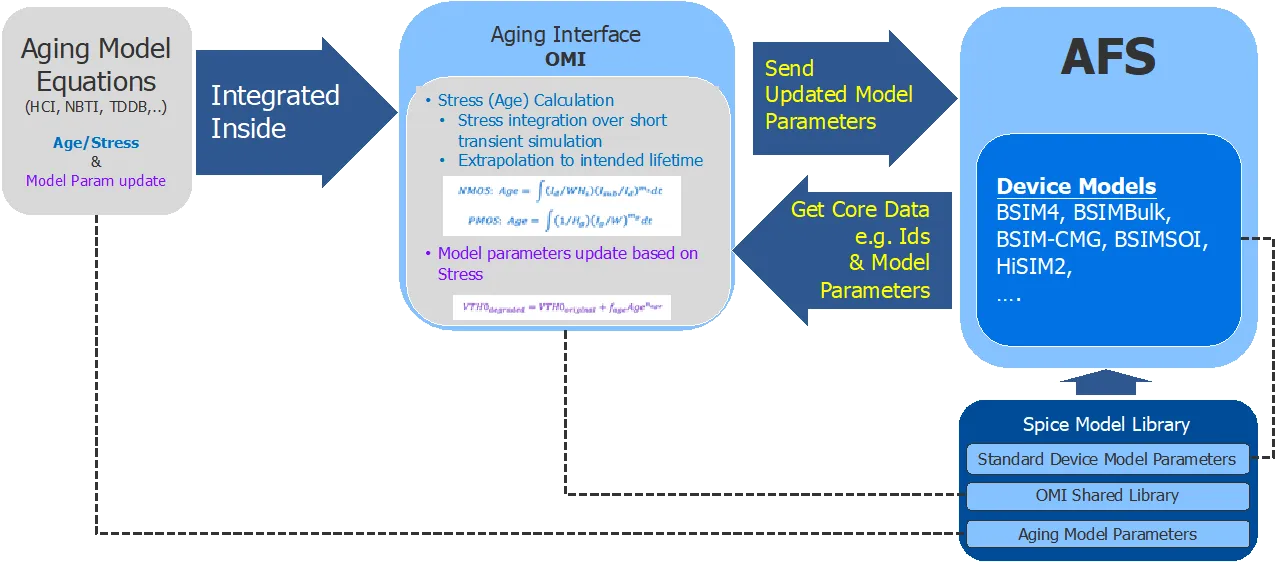

This article highlights how Mentor and Samsung are working together to ensure Qualcomm and other customers develop a successful product development roadmap with strong support for design automation, quality, and product reliability across all process technology nodes from planar technology to FinFET technology and beyond. The author explains why the Open Model Interface (OMI) is a standard solution and how the OMI model was verified with Analog FastSPICE (AFS), Mentor’s nm-accurate SPICE simulator, and other simulators in terms of accuracy and performance.

This article highlights how Mentor and Samsung are working together to ensure Qualcomm and other customers develop a successful product development roadmap with strong support for design automation, quality, and product reliability across all process technology nodes from planar technology to FinFET technology and beyond. The author explains why the Open Model Interface (OMI) is a standard solution and how the OMI model was verified with Analog FastSPICE (AFS), Mentor’s nm-accurate SPICE simulator, and other simulators in terms of accuracy and performance.

Oren Manor: Mentor Leading Way for Industry 4.0

iConnect007

In this article, Oren Manor talks about the integration of Mentor’s CAD/CAM solutions with Siemens’ mechanical offerings, Industry 4.0 and more.