Article Roundup: The 5th Global Mega Trend, Optimizing for USB 3, Preparing for New Nodes, Managing Design Rules & FPGA Verification

- Roland Busch, COO & CTO of Siemens: The Fifth Mega Trend That Is Changing Siemens’ Future

- Optimize USB 3 by Understanding How it Works

- Preparing for success at the next node with Calibre

- Mentor’s EDA Perspective on Managing Design Rules

- FPGA And System Designs Get To Market Faster Leveraging ASIC-Proven Analysis Tools

Roland Busch, COO & CTO of Siemens: The Fifth Mega Trend That Is Changing Siemens’ Future

Forbes

Siemens has identified a fifth global mega trend that is shaping the world today: digitalization. Along with urbanization, globalization, aging populations, and climate change, digitalization expands across industries and verticals. In this interview, Roland Busch, COO & CTO of Siemens, explains how the company is preparing for a digitalized world.

Siemens has identified a fifth global mega trend that is shaping the world today: digitalization. Along with urbanization, globalization, aging populations, and climate change, digitalization expands across industries and verticals. In this interview, Roland Busch, COO & CTO of Siemens, explains how the company is preparing for a digitalized world.

Optimize USB 3 by Understanding How it Works

Electronic Design

The invention of USB twenty years ago vastly simplified the use of peripheral devices with personal computers. Under this simplicity, however, is a complex technology. When designing an embedded system, a basic understanding of how USB works is very helpful for the embedded software engineer.

The invention of USB twenty years ago vastly simplified the use of peripheral devices with personal computers. Under this simplicity, however, is a complex technology. When designing an embedded system, a basic understanding of how USB works is very helpful for the embedded software engineer.

Preparing for success at the next node with Calibre

Tech Design Forum

The push towards new semiconductor process nodes requires all members of the supply chain to continually improve and innovate. This article examines how Mentor works with partners to prepare each version of its Calibre DFM platform for the introduction of new process nodes.

Mentor’s EDA Perspective on Managing Design Rules

I-Connect 007

EDA companies help their customers use design constraints to effectively boost performance without ballooning the cost of the board or creating a manufacturing headache. Dave Wiens and Mike Santarini discuss how Mentor views design rules and advises customers.

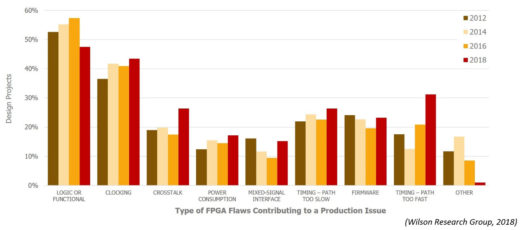

FPGA And System Designs Get To Market Faster Leveraging ASIC-Proven Analysis Tools

SemiEngineering

Power constraints on digital designs are growing. To meet tight power budgets, designers create smaller functional blocks that can disable their clocks, or power down entirely. As a result, clocking issues are becoming more prevalent in FPGA and system verification. Proven tools from the ASIC design community are readily applicable to FPGA verification, enabling engineers to meet tight deadlines and manage complexity.

Power constraints on digital designs are growing. To meet tight power budgets, designers create smaller functional blocks that can disable their clocks, or power down entirely. As a result, clocking issues are becoming more prevalent in FPGA and system verification. Proven tools from the ASIC design community are readily applicable to FPGA verification, enabling engineers to meet tight deadlines and manage complexity.