Advantages Of Using Tessent Shell For LogicBist Built-in Self Test Implementation

Logic Built-In Self-Test (LogicBIST/LBIST) embeds test circuitry directly within a chip, making it an essential feature for modern integrated circuit design. By enabling faster, more efficient testing and diagnosis, LogicBIST not only boosts reliability during manufacturing but also helps ensure ongoing performance throughout the chip’s operational life. As designs become more complex, LogicBIST provides a streamlined way to enhance test coverage and reduce debug time, ultimately speeding up time-to-market.

Key features and benefits of LogicBIST include:

- On-Chip Testability: By integrating test circuitry directly into the chip, LogicBIST enables the internal logic of the chip to be tested without relying on external test equipment extensively.

- Reduced Test Costs: It helps in reducing the cost associated with test equipment and test time because many tests can be performed internally by the chip itself.

- Improved Fault Coverage: LogicBIST can improve the detection of faults within the chip by providing specific tests that target various aspects of the circuit’s functionality.

- Dynamic Testing: Unlike traditional static testing methods, LogicBIST can perform tests dynamically during the operation of the chip, which can help in detecting faults that might occur during normal operation.

- Built-In Diagnosis: It often includes diagnostic features that help in pinpointing the location and nature of faults detected during testing, which aids in subsequent debugging and maintenance.

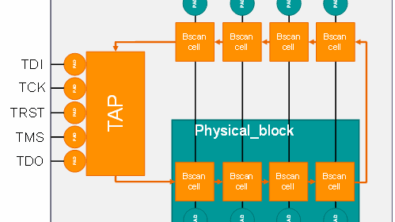

The Tessent Shell EDA tool fully supports LogicBist implementation starting from initial RTL creation inserted into your design to LogicBist Fault simulation. The generated patterns can run on the tester as well as during functional chip operation using InSystemTest (sometimes called Mission Mode). The advantage of using Tessent Shell is that is incorporates the Hybrid TK/LBIST flow, which combines capabilities from different tools (LogicBist and TestKompress (EDT) to optimize the testing of integrated circuits (ICs). Sharing Tessent EDT and Tessent LogicBIST IP functionality reduces hardware overhead. You can implement hybrid TK/LBIST as a dofile or specification-based flow, depending on how the command files are written, and as bottom-up or top-down, depending on the IP implementation.

Let’s break down the key components and concepts involved:

- Tessent Shell: This is a platform provided by Mentor Graphics (now Siemens EDA) for comprehensive IC testing and validation. It integrates various tools and methodologies to facilitate efficient design for testability (DFT) and manufacturing test solutions.

- LogicBIST (LBIST): Logic Built-In Self-Test is a technique where test circuitry is embedded within the IC itself to perform tests and diagnostics. It helps in detecting faults and verifying functionality without relying heavily on external test equipment.

- TestKompress (TK): This is a tool within the Tessent suite that provides capabilities for test compression and test pattern generation. It helps in reducing test data volume and test application time, which are critical in high-volume manufacturing environments.

- Hybrid TK/LBIST Flow: This flow combines the functionalities of TestKompress (TK) with Tessent LogicBIST (LBIST) within the Tessent Shell environment. The goal is to leverage the strengths of both TK and LBIST to achieve efficient and effective testing while minimizing hardware overhead and optimizing test coverage.

- Shared IP Functionality: By sharing functionalities between TestKompress and Tessent LogicBIST IP, the hybrid flow aims to reduce duplication and optimize resource utilization on the IC.

- Implementation Flexibility: The hybrid TK/LBIST flow can be implemented in different ways:

- Dofile or Specification-Based Flow: This refers to how command files are structured and executed within Tessent Shell to define and execute the test flow.

- Bottom-Up or Top-Down Approach: This depends on the design and implementation strategy for integrating TK and LBIST IP functionalities into the IC. A bottom-up approach typically starts with lower-level components, while a top-down approach begins with higher-level design elements.

In summary, the hybrid TK/LBIST flow in Tessent Shell combines TestKompress and Tessent LogicBIST functionalities to optimize IC testing. It provides flexibility in implementation and leverages shared IP functionalities to improve efficiency and reduce hardware overhead in semiconductor testing processes.

For more information on the hybrid TK/LBIST flow, refer to the official Tessent LogicBist Website

Also, refer to the following references in the Tessent Support Center:

Hybrid TK/LBIST Flow User’s Manual

Increase Fault Coverage and Reduce Test Time with Observation Scan in your LogicBist Flow

Observation Scan Technology (OST) implementation using the Basic Tessent shell Specification Flow

For more Support and training information on Tessent MBIST solutions, please refer to Support Center https://support.sw.siemens.com and Siemens’ Xcelerator Academy Siemens Xcelerator Academy

Register to our upcoming EDA Expert Series Webinar