6 frequent design rule checking errors every IC designer should know – and how Calibre nmDRC helps you avoid them

By John Ferguson

When design rule checking becomes the make-or-break moment

Every integrated circuit designer eventually reaches the same tense moment: that last design rule check before tape-out.

– If it passes, the layout heads to manufacturing.

– If it fails, days or weeks of rework can delay schedules and burn resources.

Design rule checking (DRC) is the final gate between design intent and manufacturable silicon. It verifies that every layer in a layout follows the geometrical and connectivity constraints defined by the foundry—rules refined through years of process characterization.

But the truth is, not all design rule checking runs are created equal. The accuracy of the results depends entirely on the engine behind the rule deck. And that’s why Calibre nmDRC remains the trusted foundation for accurate, high-performance physical verification.

Let’s explore six DRC error types that appear frequently—and how Calibre nmDRC gives designers the visibility, precision and control to resolve them well before final sign-off by fixing gross errors throughout the design process.

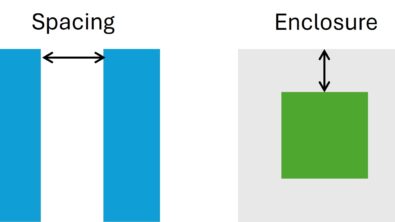

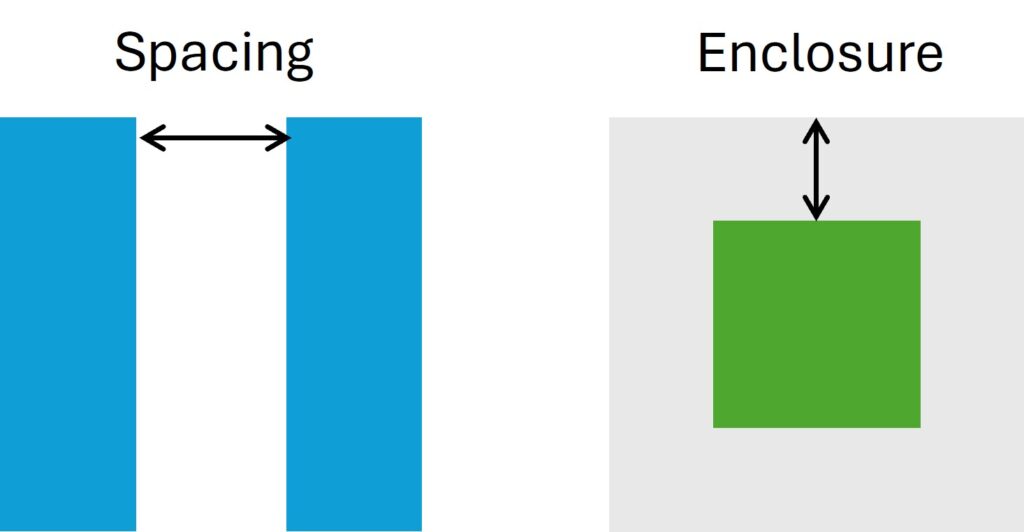

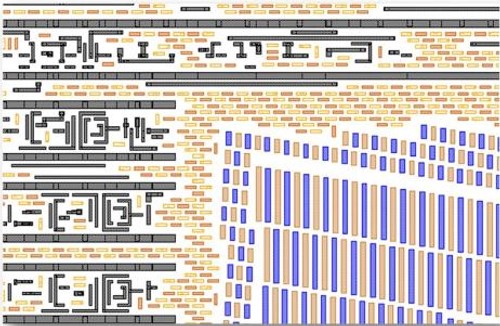

1. Metal spacing and enclosure violations

At nanometer dimensions, even the smallest geometric discrepancy can have major yield consequences. Spacing and enclosure violations occur when two shapes are placed too close together or when one layer (for example, a contact) is insufficiently enclosed by another (such as metal).

These checks sound simple but quickly become complex. Advanced rules often depend on local context—width-dependent spacing, multi-layer interactions and even stress or topography effects.

How Calibre nmDRC helps

- A geometry engine optimized for nanometer precision measures exact distances and overlaps, even in highly curved or non-Manhattan layouts.

- Hierarchical verification ensures that spacing checks scale efficiently, no matter how many repeated cells a design contains.

By combining rule-driven and equation-based approaches, Calibre nmDRC captures both deterministic and conditional spacing behaviors—so nothing slips through.

2. Density and fill errors

Chemical-mechanical polishing (CMP) demands consistent surface density across each layer. Uneven pattern densities can cause over- or under-polishing, leading to metal dishing or dielectric erosion.

How Calibre nmDRC helps

- Integrated density window checking quantifies metal coverage across the layout to ensure compliance with foundry thresholds.

- Calibre YieldEnhancer with SmartFill automatically inserts model-based fill patterns that achieve uniformity, calling Calibre nmDRC to ensure that the fill doesn’t compromise timing or violating other spacing rules.

- Back-annotation of SmartFill data to, LEF/DEF, OpenAccess, OASIS and GDSII ensures downstream extraction and simulation reflect the final filled layout accurately.

For complex SoCs, SmartFill and nmDRC operate as a single ecosystem—analyzing density, inserting fill and verifying the results in one continuous flow.

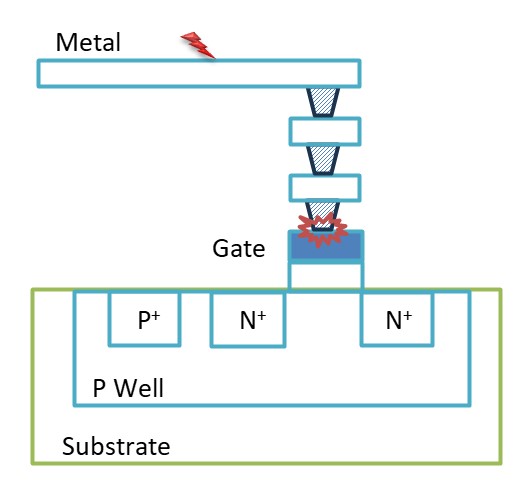

3. Antenna effects

As transistors shrink, thin gate oxides become increasingly vulnerable to plasma charging during fabrication. Long interconnects can accumulate charge and discharge into gates, permanently damaging the device.

- Dedicated antenna rule checks calculate precise metal-to-gate area ratios per process rules to check for transistor failures that can happen during the manufacture process when charge is induced on the metal wires.

- eqDRC property filtering provides numeric feedback, highlighting nets that exceed thresholds. eqDRC is an operation of SVRF (standard verification rules format).

- Annotated error markers guide designers directly to problem nets in Calibre RVE within their custom or automated design tools.

These checks are essential in high-voltage, analog or RF layouts, where antenna sensitivity varies across nets. With Calibre nmDRC, engineers can measure, visualize and correct antenna risk with confidence.

4. Via and contact misalignment

Each via that connects one metal layer to another represents a potential failure point. Even slight misalignment or insufficient enclosure can create high-resistance contacts or opens—defects that are nearly impossible to fix post-silicon.

How Calibre nmDRC helps

- Direct database access allows the design rule checking engine to read native layout formats (Milkyway, LEF/DEF, OpenAccess, OASIS, GDSII) without conversion, preserving layer precision.

- Hierarchical checking reuses data for repeated via structures, reducing runtime without sacrificing accuracy.

Calibre nmDRC’s precision ensures that every via meets the foundry’s geometry and overlay requirements, even in dense interconnect stacks.

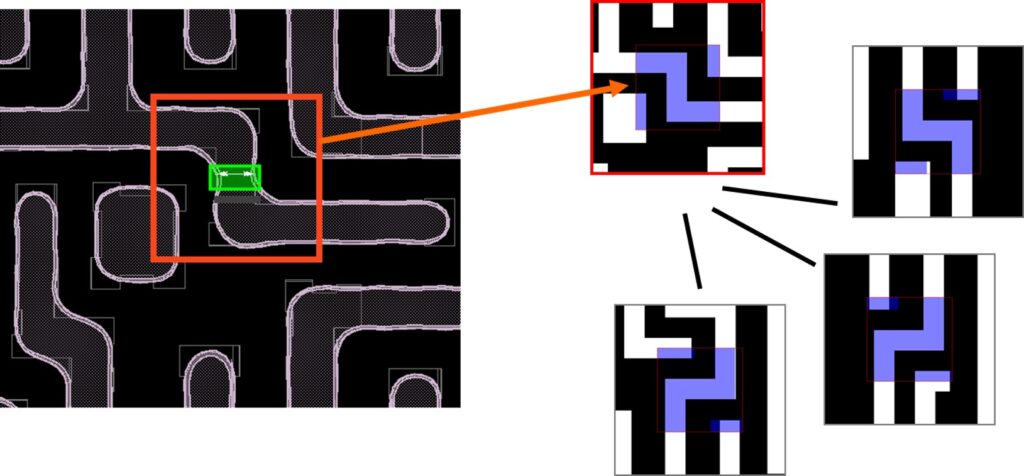

5. Pattern-based hotspots

Some yield-limiting issues aren’t easily captured by rule statements at all. They arise from specific geometric configurations—for instance, line-end bridges, notch corners or complex multi-layer patterns that interact poorly during lithography.

How Calibre nmDRC helps

- Pattern Matching technology, built directly into the nmDRC engine, searches for known problematic shapes within the same rule deck used for traditional DRC.

- Foundries often include these pattern libraries in their sign-off decks, giving designers the same predictive insight used during process qualification.

- Multi-patterning and optical-grid checks further expand coverage to lithography-driven constraints below 28 nm.

By integrating pattern analysis directly with rule checking, Calibre nmDRC enables a single unified flow that covers both standard and context-sensitive geometries.

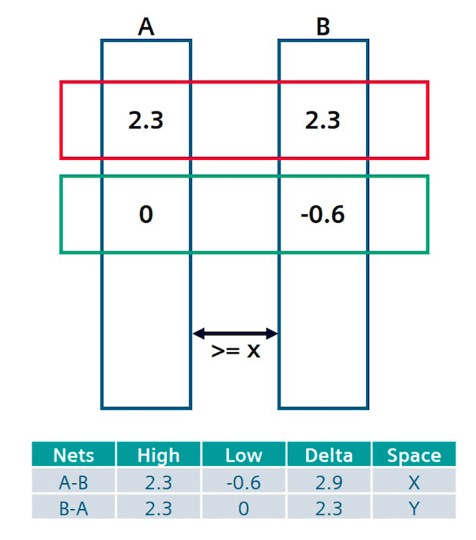

6. High-voltage checks

High-voltage checks are essential for designs with significant voltage differences, like power management units, where standard geometric spacing isn’t enough. They ensure that adjacent metal lines have sufficient clearance based on their potential difference, preventing electrical breakdown, arcing and reliability issues.

How Calibre nmDRC helps

- Voltage-aware rule application with DFM DV: Calibre nmDRC, leveraging its Design for Manufacturability (DFM) Design Verification (DV) capabilities, dynamically applies spacing rules that vary based on the voltage difference between adjacent nets. This goes beyond static geometric checks to intelligent, electrically-aware verification.

- Integrated net property analysis: It seamlessly integrates netlist information, including voltage assignments, directly with the physical layout data. This allows Calibre nmDRC to precisely calculate potential differences and apply corresponding high-voltage spacing requirements.

- Comprehensive breakdown prevention: Foundries can define intricate high-voltage rule sets within Calibre nmDRC, enabling designers to verify that their layouts meet stringent electrical isolation requirements, preventing costly field failures and ensuring product safety.

With Calibre nmDRC, designers can confidently tackle the complexities of high-voltage integration, knowing their designs are robust against electrical breakdown and meet critical reliability standards.

Beyond finding errors: fixing them faster

Catching a violation is only half the job—the real value lies in how quickly it can be understood and corrected.

Calibre nmDRC includes advanced debugging and reporting capabilities designed to shorten this loop dramatically.

Key productivity features

- Calibre Vision AI is a powerful debugging environment that uses AI to identify systematic issues and address the most impactful errors early.

- Calibre RVE provides interactive cross-probing between error markers and layout shapes.

- Customizable HTML batch reports let engineers pre-screen, sort and filter errors to focus on critical categories.

- Engineers can group results by user-defined attributes, embed snapshots and even use colormaps or histograms to illustrate violation distribution.

- Automated Waiver Management removes pre-approved exceptions from subsequent runs, keeping reports clean and traceable.

These capabilities make physical verification review cycles faster, more visual and more collaborative—an essential advantage for large, distributed design teams.

Shift-left design rule checking: catching problems earlier

Waiting for a full sign-off run to reveal thousands of errors late in the schedule is no longer practical. To compress verification cycles, design teams are moving design rule checking earlier in the layout process—a methodology known as shift-left verification.

Calibre nmDRC Recon makes that shift tangible.

It executes targeted, early-stage DRC runs using partial rule subsets, giving designers instant feedback as they edit layouts.

Because Recon uses the same Calibre rule syntax and geometry engine as sign-off DRC, results correlate perfectly—eliminating redundant debugging at the end of the flow.

Early design rule checking visibility means fewer late-stage surprises, faster convergence and better collaboration between layout and verification teams.

Why foundries and designers trust Calibre nmDRC

Every check discussed above—spacing, density, antenna, via and pattern analysis—relies on consistent correlation between design and manufacturing. That consistency exists because foundries build their rule decks in Calibre nmDRC.

- Used by the vast majority of major foundries for process development and validation

- Provides comprehensive, accurate and proven sign-off physical verification across all technology nodes

- Offers fast, scalable runtime from single CPU to enterprise compute grids

- Supports direct database access to major design formats without data conversion

- Delivers enhanced DRC debugging for faster results with highest accuracy

In short, the same tool that defines the rules is the one verifying your layout—closing the loop between process development and design implementation.

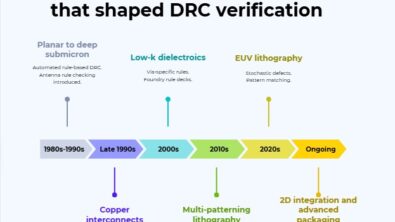

A culture of continual innovation

Calibre nmDRC doesn’t stand still

As design geometries evolve, Siemens EDA’s Calibre team continually extends the platform with new methodologies—optical grid and pitch checking, equation-based analysis, model-based fill and 3D IC verification.

This commitment ensures that the tool remains ahead of emerging process challenges and ready for the next generation of nodes.

When the industry moved to multi-patterning, Calibre nmDRC already had decomposition analysis.

When designers needed faster comparisons, Calibre Fast XOR made layout-versus-layout checks near-instant.

And as DRC debugging became more data-intensive, customizable HTML reporting and database-level visualization brought clarity and speed to complex error analysis.

That steady pace of innovation, and deep partnerships throughout the semiconductor ecosystem, keeps Calibre nmDRC aligned with the needs of modern IC design.

Conclusion: The design rule checking standard for first-pass silicon

Design rule checking remains the most fundamental measure of a design’s manufacturability.

But in an era of exploding rule complexity and shrinking process windows, trusting your DRC results is just as important as passing them.

By combining foundry-certified accuracy, advanced rule characterization, hierarchical scalability and unmatched debug visibility, Calibre nmDRC enables engineers to move from violation discovery to resolution with maximum efficiency.

It’s more than a DRC tool—it’s the verification standard that connects design, manufacturing and innovation.

When it’s Calibre-clean throughout the design stages, it’s truly sign-off-ready.