Establishing a reliability baseline provides confidence and consistency

By Matthew Hogan – Mentor, A Siemens Business

Design companies must establish baseline robustness and reliability criteria throughout the entire design, from IP to full-chip. Using a foundry reliability rule deck is a good start.

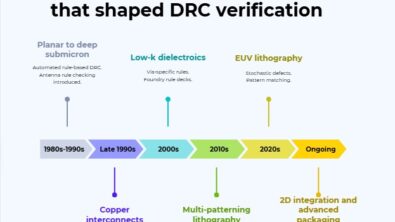

Automated reliability verification is rapidly being added to everyone’s checklist, as the market demand for dependable electronics that can perform in always-on, automotive, high-stress environments and critical use applications expands. Automation of both reliability and design consistency checks replaces manual inspection, which is time-consuming and error prone, with an efficient, consistent, and repeatable reliability verification process. One big assist in this transition is the many foundries who now offer reliability rule decks leveraging automated reliability verification. These foundry rule decks create a baseline for reliability acceptance throughout the entire design flow, from IP to full-chip reliability applications. In addition to providing this baseline, they make it much easier for engineers to understand how to apply the precise rules of a new process node. Design companies with access to a foundry-supported reliability rule deck now have a new level of confidence that complex reliability susceptibilities in their designs can be found, analyzed, and properly corrected during verification.

Of course, while these foundry rule decks (many of which leverage the capabilities of the Calibre® PERC™ reliability platform) are a great place to start for developing a reliability baseline, there may also be occasions where, just as in the case of foundry-provided DRC checks, verification teams or designers choose to augment these checks, based on the target industry and the expected customer use profile of their product. Custom checks are often used to verify the reliability of analog device constraints, custom electrostatic discharge (ESD) devices and related interconnect, along with enhancements in the field of latch-up verification. For many, the foundry-provided ESD/latch-up rules serve well as sign-off criteria, but depending on what your foundry provides, additions to your full-chip checklist might need to include:

- Validation that all IPs are correctly implemented

- Latch-up protection verification

- Voltage-aware DRC checking

- Interconnect robustness analysis

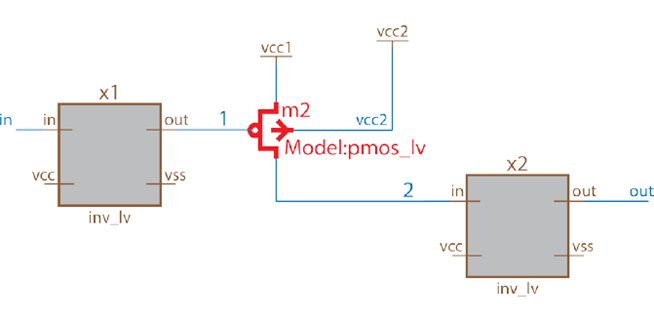

- Stacked devices analysis in the context of the whole chip

- Verification that the correct power ties are used in wells

In all cases, establishing a baseline reliability verification process provides multiple benefits to design companies. A clear understanding of how well a design will perform in a given use model is essential for making good (and consistent) architectural and design choices.

Intellectual property (IP) re-use, whether it is IP developed internally for previous projects or sourced externally, contributes a significant portion to today’s designs. A significant challenge for this re-use is the determination of suitability. IP from multiple sources are likely to contain different design styles and techniques. Identifying these differences early in the design process helps eliminate issues during IP integration and assembly that can destroy delivery schedules. For example, one reliability design decision where consistency across teams is valuable is the choice of which ESD techniques to use for IO pin protection.

Comprehensive verification at the full-chip level is an equally important consideration. Rule decks used for both IP and full-chip runs often have settings or modes that are used to define the verification level to create the appropriate results. Overall chip context is an important aspect of validating critical reliability applications, including ESD, electrical overstress (EOS), voltage-aware DRC, and interconnect robustness checking, which can be particularly critical for avoiding charge device model (CDM) issues.

With an extensive set of foundry-supported rule decks available, the Calibre PERC platform provides a wide range of automated checking capabilities focused on reliability challenges for the foundry and designers alike. The ability to add customized checks to this baseline delivers complete coverage for both the foundry and internal reliability rule decks. To learn more about establishing a baseline automated reliability verification solution, and how Calibre tools can help, download a copy of our white paper, Leveraging Baseline Checks for Robust Reliability Verification