Calibre Collaboration and Innovation on Display at TSMC OIP Santa Clara

At the TSMC Open Innovation Platform® (OIP) event in Santa Clara on September 13, Mentor was privileged to co-present with three of its customers. In all three cases, collaboration and cooperation between TSMC, Mentor, and the customer enabled the development of innovative design verification solutions that improve both the quality of designs delivered to TSMC and the productivity of the design company. A key element of the Open Innovation Platform is the set of ecosystem alliances and collaborative components initiated and supported by TSMC that more efficiently empower innovation throughout the supply chain.

At the TSMC Open Innovation Platform® (OIP) event in Santa Clara on September 13, Mentor was privileged to co-present with three of its customers. In all three cases, collaboration and cooperation between TSMC, Mentor, and the customer enabled the development of innovative design verification solutions that improve both the quality of designs delivered to TSMC and the productivity of the design company. A key element of the Open Innovation Platform is the set of ecosystem alliances and collaborative components initiated and supported by TSMC that more efficiently empower innovation throughout the supply chain.

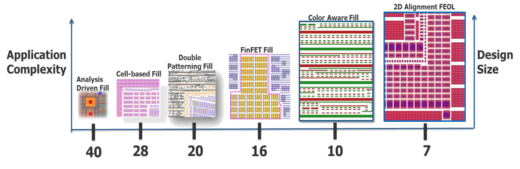

John Waida, Senior Staff Engineer at Qualcomm, teamed up with Jeff Wilson, the Marketing Director for Calibre DFM, to discuss how Qualcomm used the SmartFill fill solutions provided by the Calibre® YieldEnhancer tool to meet Qualcomm’s design objectives, while also satisfying TSMC’s density and physical design rules at multiple process nodes. Qualcomm used Mentor’s SmartFill technology to develop their FillPlus supplemental fill methodology.  FillPlus helps Qualcomm meet all TSMC requirements while minimizing both timing impacts to the design and runtime impacts to the design flow. Equally important, the FillPlus solution is a simple add-on to their design flow that can be used only when necessary. Because the SmartFill technology is the plan of record at TSMC (meaning it is the fill tool TSMC uses during process development), Qualcomm can easily stay on top of the latest changes in fill requirements during advanced node design. Although Qualcomm experimented with other fill options, in the end, this team decided the SmartFill technology from Calibre was the only solution that enabled them to meet their design flow goals and satisfy TSMC’s tapeout requirements at every process node.

FillPlus helps Qualcomm meet all TSMC requirements while minimizing both timing impacts to the design and runtime impacts to the design flow. Equally important, the FillPlus solution is a simple add-on to their design flow that can be used only when necessary. Because the SmartFill technology is the plan of record at TSMC (meaning it is the fill tool TSMC uses during process development), Qualcomm can easily stay on top of the latest changes in fill requirements during advanced node design. Although Qualcomm experimented with other fill options, in the end, this team decided the SmartFill technology from Calibre was the only solution that enabled them to meet their design flow goals and satisfy TSMC’s tapeout requirements at every process node.

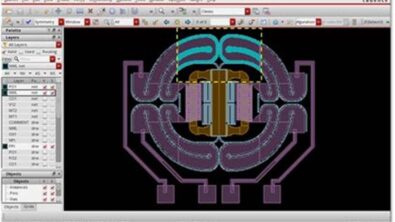

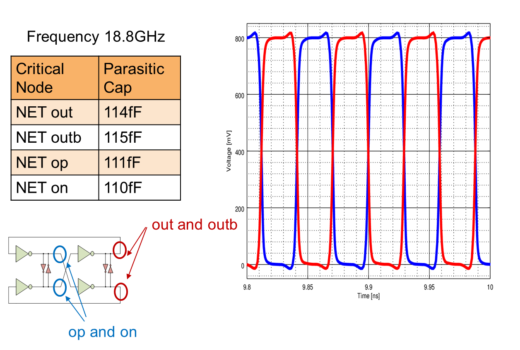

At eTopus Technology, the focus is on products for the enterprise network, data center, and high-performance computing markets. As a pioneer of ADC/DSP-based SerDes, eTopus relies on the integration of sensitive analog/mixed-signal (AMS) elements within the context of complete designs, as well as the use of three-dimensional finFET transistors, to attain the performance and power goals that define their products.  Because extraction is an important part of ensuring those goals are met, eTopus implemented the innovative parasitic extraction technology in the Calibre xACT™ platform. Christopher Clee discussed Mentor’s unique hybrid approach in the Calibre xACT platform that automatically delivers the right extraction solution for each part of a design, enabling field solver accuracy where needed, while providing fast rule-based extraction for the rest of the design. Shahab Ardalan of eTopus then demonstrated how they used the Calibre xACT solution to overcome some of the specific extraction challenges presented by the design of a ring VCO, highlighting the flow from their custom design tools through parasitic extraction into simulation.

Because extraction is an important part of ensuring those goals are met, eTopus implemented the innovative parasitic extraction technology in the Calibre xACT™ platform. Christopher Clee discussed Mentor’s unique hybrid approach in the Calibre xACT platform that automatically delivers the right extraction solution for each part of a design, enabling field solver accuracy where needed, while providing fast rule-based extraction for the rest of the design. Shahab Ardalan of eTopus then demonstrated how they used the Calibre xACT solution to overcome some of the specific extraction challenges presented by the design of a ring VCO, highlighting the flow from their custom design tools through parasitic extraction into simulation.

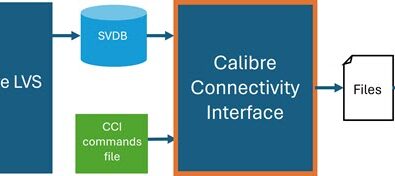

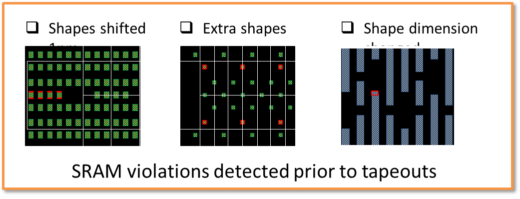

As every SoC designer knows, traditional SRAM verification flows require significant resources to implement and support, and can still miss subtle, but critical, layout modifications that result in manufacturing challenges for foundries. Developing rule checks to perform every precise intra-cell design measurement, and check every inter-layer, inter-cell, orientation restriction, and multi-patterning requirement makes advanced node SRAM verification a major challenge. TSMC collaborated with Mentor to develop an innovative SRAM IP checking methodology leveraging the Calibre SVRF language and the Calibre Pattern Matching tool, ensuring the highest manufacturability. By creating a methodology that leverages pattern matching in conjunction with existing rule-based solutions to detect approved cell configurations, TSMC achieves complete coverage of every SRAM IP placement. Patterns simplify the rule descriptions of each layer interaction, and provide efficient rule coverage and richer error visualization. Jonathan Muirhead from Mentor highlighted SRAM IP layout modifications commonly faced by foundry OPC teams, and presented one of the industry’s first complete pattern-based SRAM verification and error identification flows, built upon Calibre Pattern Matching technology.

MediaTek is one of the largest system-on-chip (SoC) providers in the market, supplying SoCs for virtually every electronics application, from smartphones to GPS systems to AP routers, and even machine to machine systems. As a fabless company, they partner with TSMC to produce their chips. Dar-Shii Chou of MediaTek demonstrated how their use of TSMC’s SRAM checker pattern-based solution provides a fast, scalable solution preventing potential manufacturing risk and eliminates the previous iterations with TSMC to revise SRAM macros.

MediaTek is one of the largest system-on-chip (SoC) providers in the market, supplying SoCs for virtually every electronics application, from smartphones to GPS systems to AP routers, and even machine to machine systems. As a fabless company, they partner with TSMC to produce their chips. Dar-Shii Chou of MediaTek demonstrated how their use of TSMC’s SRAM checker pattern-based solution provides a fast, scalable solution preventing potential manufacturing risk and eliminates the previous iterations with TSMC to revise SRAM macros.

By bringing customers and ecosystem partners together to share their collaboration successes, TSMC’s Open Innovation Platform events help move the industry toward the common goals of reducing design time, minimizing time-to-volume, speeding time-to-market, and ultimately shortening time-to-money.

As the day came to a close, we spoke with Michael Buehler-Garcia, senior director of marketing for Calibre Design Solutions. Asked about the value of the Open Innovation Platform to Mentor, he responded, “TSMC’s long-standing collaboration with Mentor enables both companies to work together effectively to identify new challenges and develop innovative solutions across all process nodes and design technologies. By working closely with TSMC, Mentor can provide our mutual customers with solutions that are not only certified, but also include the latest tool capabilities, for whichever TSMC process node they use.”