Design rule checking in today’s integrated circuit design environment

By John Ferguson, Senior Director of Product Management, Siemens EDA

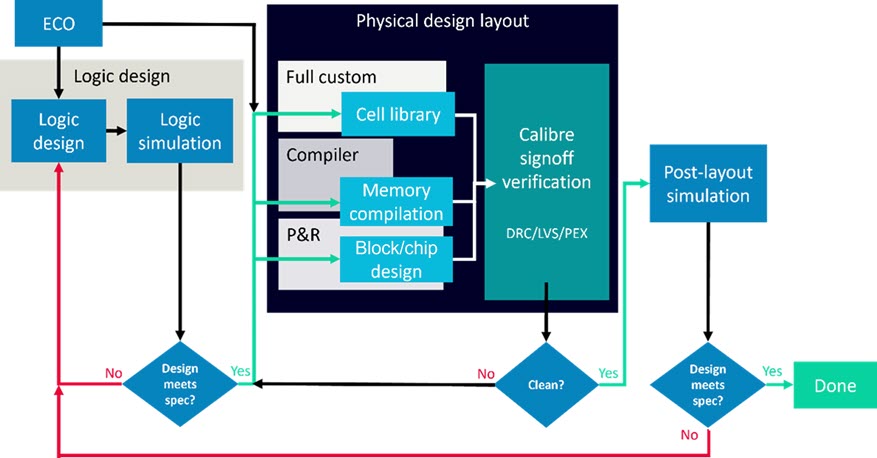

Today’s integrated circuit (IC) designs face rising complexity, massive scale and tighter timelines, pushing engineers to rethink how they approach every stage of the flow. At the heart of successful tapeouts lies design rule checking (DRC)—a critical verification step that ensures layouts comply with foundry manufacturing constraints.

What was once a routine sign-off process has become a growing challenge. Shrinking geometries, advanced patterning and increasingly complex rule decks have driven up both runtime and engineering overhead. Designers must now balance the dual pressures of delivering faster while verifying more thoroughly.

This blog explores how integrated circuit design rule checking is adapting to today’s environment, why Calibre nmDRC Recon is reshaping early-stage verification strategies and where the industry is headed.

Back to basics: What is design rule checking?

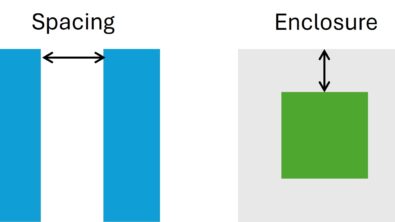

At its core, integrated circuit DRC the automated process of validating a chip layout against a set of foundry rules. These rules govern geometry spacing, width, enclosure, density and countless other constraints that impact manufacturability.

- Primary purpose: Detect layout errors before fabrication.

- Scope: From transistor-level features at advanced nodes.

- Result: A sign-off report that confirms a design is manufacturable.

In practice, the integrated circuit design rule check is performed using tools like Calibre nmDRC, an industry standard for sign-off physical verification.

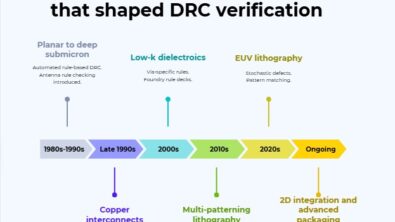

The evolving IC design landscape

As semiconductor technology progresses, the role of DRC has expanded beyond a simple verification step. In the past, DRC involved a few hundred relatively straightforward geometric checks. Today, it requires far more complex operations, with many interdependent tasks that have led to an explosion in the total number of checks. Modern DRC must adapt to new design styles, larger chip architectures and the growing need for early verification feedback. Understanding these shifts provides context for why both sign-off and fast-feedback approaches are essential today.

1. Increasing architecture complexity

Modern design practices—spanning areas like 3D ICs, photonics and even emerging quantum compute—are introducing far more complex and curved geometries into layouts. This evolution pushes design rule checking beyond traditional planar verification, demanding more sophisticated techniques to ensure results are captured with accuracy across these advanced architectures.

2. Performance vs. cost tradeoffs

Shrinking geometries improve performance and density but also raise verification costs. Foundry rule decks can contain millions of checks, leading to longer runtimes and larger memory footprints.

3. Verification scale and strategy

Traditional full-chip design rule checking remains the gold standard for sign-off, ensuring complete compliance with foundry requirements. However, its comprehensive nature also means longer runtimes. Complementary approaches like Calibre DRC Recon provide a faster way to catch common violations earlier in the process, reducing the number of full sign-off iterations required.

4. Placement-driven errors in automated layouts

Today’s layouts are largely automated through place-and-route (P&R) tools. That automation accelerates design but also concentrates errors in specific regions. Often, violations aren’t isolated individual issues—they stem from broader placement or floorplanning problems. Instead of addressing every single spacing or density violation one by one, engineers can focus on fixing the underlying placement conflict. By correcting a single misaligned region, they may eliminate an entire cluster of errors at once, saving time and reducing debug fatigue.

Calibre nmDRC & Calibre DRC Recon

| Aspect | Traditional DRC (Sign-off) | DRC Recon (Early-stage) |

| Purpose | Comprehensive, foundry-certified sign-off | Early detection of gross violations |

| Rule Coverage | Full rule deck (millions of checks) | Subset of rules, focused on common issues |

| Runtime | Hours to days | Minutes |

| Use Stage | Final verification before tapeout | Iterative checks during layout creation |

Calibre nmDRC Recon provides a fast, lightweight complement to sign-off DRC. By running a reduced rule set, it enables designers to identify major violations—such as spacing errors or density issues—early in the flow, without waiting for full verification. The reduced rule set is automatically detected using AI heuristics based on what checks are likely to have ‘local scope’, where a relatively small area needs to be analyzed. This speeds up the DRC runs, and more importantly, clusters the results close to the root-cause of the problem, which helps the designers to more quickly pinpoint and fix the problem.

The true value of Calibre nmDRC Recon lies in reducing the number and duration of design iterations, not just speeding up each run. In a traditional design flow, initial data is very dirty, so any DRC verification run would be slow and produce a huge number of errors. Designers then have to address individual errors equally because there is no way to prioritize problems that should be fixed early, like power-ground shorts and multi-patterning problems.

Calibre nmDRC Recon clusters errors by region, often pinpointing areas near the root cause, such as a poorly placed cell. Fixing these early can eliminate many thousands of related errors at once, so subsequent runs—whether full DRC or Recon—are much faster.

The results are even better if you add Calibre Vision AI to the mix. Calibre Vision AI takes the DRC analysis results in a compressed OASIS format, reducing file size and saving time. More importantly, it then applies AI diagnostics to quickly identify groups of errors, called Signals, and highlight major design flaws for rapid resolution.

For deeper insight, see Smarter DRC for complex designs: Accelerating verification with Calibre nmDRC Recon

Real-world use cases

Use Case 1: Advanced-node SoCs

At 3nm and below, sign-off DRC requires highly specialized rules for multiple patterning and EUV lithography. Running Calibre nmDRC provides the necessary accuracy, while Calibre nmDRC Recon enables fast iteration during layout refinement.

Use Case 2: Analog and mixed-signal design

Analog layouts often undergo many manual adjustments. Fast checks via DRC Recon allow engineers to experiment with device placement without waiting for long runs, boosting productivity.

Challenges in integrated circuit design rule checking

Despite significant advances in tools and methodologies, integrated circuit design rule checking presents several ongoing challenges for design teams. These challenges are rooted in the realities of modern semiconductor design — from exploding rule decks to increasing system complexity — and they directly impact cost, runtime and productivity.

1. Runtime and scalability

At advanced nodes, a single integrated circuit design rule check can involve billions of polygons and millions of rules. Even with parallelization and distributed computing, runtimes can extend into many hours or even days for full-chip verification. While this ensures manufacturing accuracy, the turnaround time can slow iterative design cycles, making it harder to meet aggressive tapeout schedules.

2. Growing rule complexity

Foundries continuously expand their design rule decks to account for advanced lithography (e.g., EUV, double/multi-patterning) and new device architectures like gate-all-around (GAA). These rules are often context-dependent, requiring conditional checks that increase verification complexity. Designers must not only run the checks but also interpret nuanced results that may involve layout-dependent effects.

3. Debug bottlenecks

Even with highly accurate tools, the sheer number of violations reported in a full integrated circuit design rule checking run can overwhelm teams. Sorting through thousands of results to find the true yield-critical errors consumes valuable engineering time. Debug is further complicated when violations cascade — fixing one issue may trigger another, creating a loop of manual investigation. This is why Siemens’ Calibre Vision AI is gaining traction, as it uses AI to classify and prioritize errors, helping engineers focus on what matters most.

4. Data management and compute resources

Large-scale SoCs can generate terabytes of verification data. Managing this data — from rule decks to error databases — places significant strain on IT infrastructure. Compute clusters, storage systems and network bandwidth must scale in tandem with verification demand, which can increase operational costs for design companies.

Advantages of integrated circuit design rule checking

While challenges exist, the benefits of modern integrated circuit design rule checking (DRC) are undeniable. Advanced verification methodologies and tools not only ensure manufacturability but also accelerate time-to-market and improve design quality.

1. Foundry-certified accuracy

At the core of DRC’s value is accuracy. Sign-off solutions like Calibre nmDRC are certified by leading foundries across every major process node, from mature planar technologies to cutting-edge 2nm gate-all-around architectures. This certification ensures that results correlate directly with manufacturing intent, giving design teams confidence their layouts will yield as expected.

3. Shift-left verification with DRC recon

By complementing sign-off DRC with fast, lightweight Calibre nmDRC Recon, design teams can detect major violations during early layout iterations. Instead of waiting days for sign-off runs, engineers can resolve obvious shorts, spacing and density issues in minutes. This “shift-left” approach reduces the number of full sign-off iterations required, helping to shorten design cycles and accelerate time-to-market.

4. Integration with debug and analysis tools

Modern platforms go beyond error reporting. For example, Calibre Vision AI applies machine learning to classify and prioritize violations, while integration with Calibre DESIGNrev provides interactive visualization. These capabilities help engineers identify root causes faster, reducing time spent filtering noise from true yield-critical errors.

5. Flexibility across design styles

Design rule checking is no longer limited to digital sign-off alone—and neither is its fast-feedback counterpart. With Calibre nmDRC Recon, setup is simple and automatic: as long as you have a working DRC deck, Recon can run. There are no design-specific tweaks, custom dependencies, or deck modifications required. This makes it easy for any team—whether working on custom analog blocks, large SoCs, or advanced 3D IC assemblies—to gain immediate manufacturability insight using the same trusted infrastructure.

Future outlook: Where DRC is headed

As IC technology continues to advance, integrated circuit design rule checking is evolving from a back-end verification step into a dynamic, intelligence-driven part of the design flow. Several trends are shaping this future, promising greater speed, scalability and insight for design teams.

1. AI-driven debug and automation

The volume of violations in advanced-node DRC runs can overwhelm engineering teams. Artificial intelligence is emerging as a powerful solution to this challenge. Calibre Vision AI demonstrates how machine learning can classify errors, identify recurring patterns and highlight the violations most likely to affect yield. This trend will reduce manual filtering and speed up debug cycles, making error management smarter and more scalable.

2. Cloud-native scalability

As designs grow into the multi-billion-transistor range, scaling verification workloads will require more than on-premises compute farms. Cloud-native deployment of design rule checking offers flexible resources that expand to meet demand. Instead of being bottlenecked by fixed server capacity, design teams can scale runs across hundreds or thousands of cloud CPUs, shortening turnaround times for sign-off DRC and enabling faster iterations of Calibre nmDRC Recon during layout.

4. Seamless shift-left adoption

Future flows will make Calibre nmDRC Recon and similar fast-feedback tools a standard part of layout creation. Instead of being a separate “early verification” step, Recon-style checking will be embedded directly into layout tools, providing real-time manufacturability guidance. This evolution will push DRC even further left in the design cycle, enabling engineers to avoid issues rather than debug them later.

5. Greater designer accessibility

Traditionally, DRC has been the domain of CAD engineers and sign-off specialists. The next wave of integrated circuit design rule checking will provide more user-friendly interfaces, integrated visualization and tighter links to layout editing environments. This democratization will give circuit and layout designers direct access to manufacturability feedback, accelerating innovation while still ensuring compliance.

Frequently asked questions (FAQ)

Q1. Why is design rule checking important in advanced nodes?

At nodes like 3 nm and beyond, manufacturing tolerances are so tight that even minor violations can cause catastrophic yield loss. DRC ensures compliance with complex lithography and patterning rules.

Q2. How does DRC impact design cost and cycle time?

Long runtimes and late discovery of violations can lead to redesigns, adding both cost and schedule risk. Early checks with tools like Recon reduce rework and shorten overall cycle time.

Q3. What are the latest trends in DRC tools?

- AI-assisted debug: Tools like Calibre Vision AI show how artificial intelligence is helping engineers classify and prioritize errors faster, reducing manual review cycles.

- Cloud-native scalability: Foundries and EDA vendors are expanding verification into the cloud, allowing dynamic compute resources to handle massive SoC verification jobs. Siemens has described this in the context of scaling sign-off flows for advanced designs.

- Shift-left adoption: With Smarter DRC for complex designs: Accelerating verification with Calibre nmDRC Recon, fast-feedback verification is becoming a standard early-stage practice, reducing rework later in the flow.

Q4. How is Calibre nmDRC Recon helping the evolving DRC landscape?

As integrated circuit designs grow more complex, Calibre nmDRC Recon delivers a fast, lightweight verification flow early in the design process. Instead of waiting until final sign-off, engineers can run targeted checks on common, high-impact rules in minutes—catching spacing errors or density violations before they multiply. This shift-left strategy reduces the number of sign-off iterations required, accelerates debug and ultimately shortens design cycles while maintaining manufacturability confidence.

Read more about Calibre nmDRC Recon Speeding up early design rule checking with Calibre nmDRC Recon

Conclusion

Design rule checking has shifted from a back-end formality to a central pillar of IC design success. With exploding complexity and shrinking geometries, designers need both comprehensive sign-off verification and fast, iterative checks earlier in the flow.

Tools like Calibre nmDRC and Calibre nmDRC Recon deliver the accuracy, speed and scalability required for today’s designs. Combined with system-level verification in Calibre Physical Verification, engineers are better equipped to balance performance, cost and manufacturability.