Calibre PERC electrical reliability verification – why you need it at every node

By Juan C. Rey, Vice President of Engineering, Calibre – Mentor, A Siemens Business

If you’re not performing electrical reliability verification on all of your designs, regardless of node, you may be missing crucial issues that affect product life and quality. Juan Rey explains why…

As the semiconductor industry moves to single-digit nanometer process geometries for chip manufacturing, it is quickly becoming mandatory that physical verification teams add electrical reliability verification to their physical verification processes. And even if your company plans to use a more mature process technology for your next chip design, it is a wise decision to add electrical reliability verification to your physical verification methodology. Here’s why…

Design Rule Checking (DRC) and Layout vs. Schematic (LVS) were historically two related but separate physical verification domains. The first is “mostly” about verifying geometrical dimensions, while the second is “mostly” about device recognition and network connectivity. As process geometries have continued to shrink, the capabilities of DRC and LVS tools have been enhanced greatly by including information provided by parasitic extraction (information regarding interconnect resistance and capacitance) and even SPICE-like simulation to enable completely new capabilities while still retaining their major accuracy and performance characteristics.

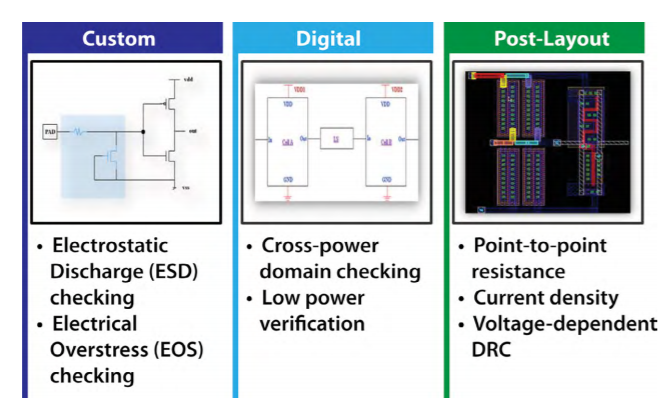

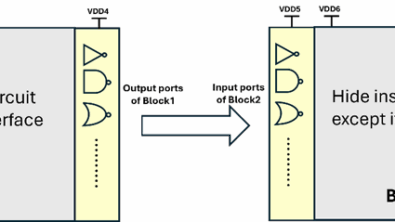

Electrical reliability verification accounts for electrical effects such as electrostatic discharge (ESD), electrical overstress (EOS), detection of signals crossing multiple power domains, advanced electrical rule checks (ERC) and other electrical reliability concerns. It is commonplace that one or many of these effects have not been adequately accounted for in the earlier design and verification steps of chip development. It is also commonplace that the foundry rules may not account for all these effects, for example, because some of them are unique to your design.

These effects are much more prevalent in the latest process technologies, which is why they are “sign-off” at 28nm and below. But if your design mandates reliability or your company maintains or wants to build a reputation for quality, you should add electrical verification to your physical verification flow even if you plan to implement your design on a more mature process. A common misperception is that mature processes do not exhibit these problems. However, if you are designing with high voltages or pushing the electrical limits of the process (as most designers are), electrical reliability should be a significant consideration. You can take the risk and assume your design is not susceptible to these effects, but you won’t know unless you verify. This also begs the question: do you know what electrical effects you are looking for and how to find them?

When test chips started to show higher than normal susceptibility to ESD and EOS at the 28 node, physical verification teams started to employ tedious manual reviews of their designs to locate issues, fix them and re-verify. This can be a cyclical, iterative and slow process, as your fixes may introduce one or more new errors.

The process of electrical reliability verification closure has been made much easier by Mentor developing the Calibre PERC tool, which works with Calibre DRC and LVS tools to automatically perform electrical reliability verification checks and achieve electrical reliability verification closure.

Specifically, the Calibre PERC tool automatically identifies complex circuit topologies on a design’s netlist, either streamed from a schematic or extracted from a layout. It then examines the specific constraints, whether they are electrical or geometrical. Then it automatically reports back as errors any discrepancy between the specifications for a particular check and the actual information in the layout under verification. And your team can customize the Calibre PERC checks to suit your particular design’s verification requirements.

To learn more in depth about achieving electrical reliability verification closure with Calibre PERC, read the white paper Leveraging Baseline Checks for Robust Reliability Verification

Comments

Leave a Reply

You must be logged in to post a comment.

I have a question about calibre perc esd verifications. does it specify esd current path in a circuit or something like this?

As with many of the Calibre products, a rule deck is used to identify what and how to verify. Please contact us for additional details.